Abstract

In this work we present, in the context of the transition from amplitude to robust spike domain sensing and electronics, a floating memristor. It can be used to construct memristor SNNs used for noise-robust conditioning and analog-to-digital conversion and manufactured using leading-edge technologies with more ’cranky’ devices, low-voltage, low power, and minimal area on-chip. Also, this supports both machine learning as well as the self-x properties in advanced sensor electronics system for industry 4.0. The proposed memristor has less design complexity and a higher number of resistance levels as compared to other existing memristors. The proposed CMOS memristor is designed using AMS 0.35 μm CMOS technology and Cadence design tools. Its layout occupies an area of 70 μm × 85 μm. The simulation shows the performance of the proposed floating memristor emulator in the temperature range (-40 °C to 85 °C) and Monte-Carlo simulation.

Zusammenfassung

In dieser Arbeit stellen wir im Kontext des Übergangs von einer Amplituden-zur robusten Pulsbereichsrepräsentation und Sensorelektronik, eine Floating-Memristor-Schaltung vor. Diese soll als Synapsenelement der Erstellung von adaptiven pulsenden Neuronennetzen dienen, die Sensorsignalkonditionierung und -nach-Digitalwandlung robust gegenüber Herstellungsschwankungen, sinkenden Betriebsspanunngen und reduziertem Aussteuerbereich, Verlustleistungs- und Flächenmimimierungsforderungen sowie Störeinflüßen erlauben und damit auch in modernsten Herstellungstechnologien mit Bauelementen sinkender Zuverlässigkeit zu lebensfähigen Sensorelektronik-Chips führen. Mit der dann gegebenen Adaptivität wird sowohl das Maschinelle Lernen unterstützt als auch die Forderung an Self-x-Eigenschaften der fortgeschrittenen Sensorelektronik für die Industrie 4.0 erfüllt. Der vorgeschlagene Memristor hat eine geringere Entwurfskomplexität und eine höhere Anzahl einstellbarer Widerstandsstufen im Vergleich zu anderen bestehenden Memristoren. Der CMOS-Memristor wurde in der AMS 0.35 um CMOS-Technologie mit der Cadence-Entwurfsumgebung entworfen. Das zugehörige Layout belegt eine Fläche von 70 μm × 85 μm. Die Simulation bestätigt die Leistungsfähigkeit der vorgeschlagenen Floating-Memristor-Schaltung im Temperaturbereich -40°C bis 85°C und einer Monte-Carlo-Analyse.’

1 Introduction

In the last few years, the number of edge devices in IoT and industry 4.0 has been increased leading to a growth in machine learning as well as the urgent need for self-x (self-healing, self-calibration) technology [1, 37, 38]. Issues of leading-edge technologies for integrated sensor electronics advocate the transition from amplitude to time or spike domain information processing. Inspirations from frequency sensors and adaptive spiking neural networks can be employed for resilient/self-x system realizations. A key mandatory element is a programmable or adaptive synapse, e.g. by a memristor realization. On the other hand, the memristor neuromorphic architectures learning, self-x, scalability, have a low power profile and small onchip footprint [20]. Currently, this technique became a promising solution for edge devices. Although many memristor neuromorphic architectures were proposed in the sensing system, however, the memristor SNNs (Spiking Neural Network) have a lower power profile and more robust to the noise since they encode the information using the spike times and process only when the events occur [31]. Also, from the mechanisms function view, since the SNNs use the time domain encoding (noise-robust) and have the capability of learning and self-x, they solve one of the main problems in the sensing system where the output noise of the sensor could lead to an indirect error in the measurements [31].

A lucid example of adaptive SNN are delay lines in acoustic localization, as shown in (Fig. 1) [14, 15, 16, 19]. The brain determines the location of the sound by the difference time of ears = t1−t2 where t1 and t2 are the times of the sound reaching the right and left ears, respectively as shown in (Fig. 1 A). The neural network in (Fig. 1 B) mimics the sound location detection by the brain. The network consists of two sensors, and each sensor represents one ear, two neurons, and two synapses. The first and the second neuron fire responds to the right and the left, respectively. The neuron spikes when the membrane voltage is greater than the threshold voltage, as shown in the (Fig. 1 B). The synapses adaptively control the amount of the charge to the neuron by adapting the spike. Consequently, the synapses control the time delay at where the neurons will be spiked. The delay can be controlled by changing the weights of the synapses. These synapses are programmed with a certain weight to keep it constant under variations/perturbations. The synapses can be emulated by a memristor with one transistor (1T1M).

(A) Acoustic localization model. (B) SNN schematic structure of equivalent conversion concept.

A memristor is a two-terminal device where the resistance value of the memristor is dependent on the polarity and magnitude of the applied voltage and the length of time that voltage has been applied [8]. As reviewed in the literature, the memristor concept was suggested by Leon Chua in 1971[8]. However, researches could not evaluate the memristor until it was implemented by Hewlett Packard (HP) in 2008 [29]. Even though many benefits gained from using the memristors in much application such as neuromorphic circuits[20], programmable analog circuits[24], chaotic circuits[23], adaptive filters[9], basic arithmetic operations[18], sensory electronics system, internet of things (IoT), machine learning[12], they are not expected to be used in the commercial chip soon because of many open problems that need tobe investigated, such as the fabrication complexity of memristor systems, unstable switching behavior, the finite number of resistor levels, and compatibility with CMOS technology [20]. To implement neuromorphic architectures and integrated on the real chips, therefore, the researchers have focused on memristor emulators [2, 3, 4, 5, 6, 10, 17, 27, 28, 30, 32, 33, 34, 35, 36]. State-of-the-art designs cannot integrate on-chip memristor because they have complex circuits and need an external devices. They are used a lot of active components and passive elements [2, 3, 4, 5, 6, 10, 17, 27, 28, 30, 32, 33, 34, 35, 36]. Some of them have grounded structures [2, 6, 10, 17, 32, 34, 35], and others have floating structures [3, 4, 5, 27, 28, 30, 33, 36]. Designing a floating memristor circuit is more complex than designing a grounded memristor circuit; however, grounded memristor has limited applications. In [17], authors proposed grounded memristor with two operational amplifiers, ten transistors, two resistors, a capacitor and multiplier. Also, in [2], they proposed grounded memristor emulator circuit using current backward transconductance amplifier (CBTA), multiplier, two resistors and a single capacitor. Additionally, in [6], they proposed grounded memristor emulator with four transistors. Likewise, in [10], he proposed grounded memristor emulator with four transistors. Similarly, in [32] he proposed grounded memristor emulator with seven transistors and a single capacitor. Moreover, in [35] they proposed grounded memristor emulator circuit using voltage differencing current conveyor (VDCC), two transistors and a single capacitor. As well, in [34] they proposed grounded memristor emulator circuit using voltage difference transconductance amplifier (VDTA), single transistors. In [28], floating memristor emulator circuit was proposed using three operational transconductance amplifiers (OTA), four second-generation current conveyors (CCII), six resistors and a single capacitor. Also, in [5] floating memristor was proposed with MO-OTA, resistor, capacitor, and multiplier. Besides, in [30] floating memristor was proposed with three transistors, external capacitor and a current source. Also, in [36] they proposed a floating memristor emulator circuit using current backward transconductance amplifier (CBTA) with two capacitors. Likewise, in [4] they proposed floating memristor with single OTA, two transistors and an external capacitor. Moreover, in [3] they proposed floating memristor with ten transistors and three external capacitors. Additionally, in [33] they proposed floating memristor emulator circuit using differential difference current conveyor (DDCC) two resistors, capacitor and multiplier. Furthermore, in [27] they proposed a floating memristor emulator circuit, which is built with four second-generation current conveyors (CCII) and single multiplier.

The primary objective of this research is to design a memristor that can be on-chip integrated without needing any external components. The target is to construct an adaptive synapse and an adaptive spiking neuron. These will serve to construct memristor-based adaptive SNNs, that introduce machine learning to support sensor electronics with self-x properties as demanded by industry 4.0.

2 Proposed Methodology

In this research, we design a compact floating memristor emulator circuit consisting of only four CMOS transistors, as shown in (Fig. 2).The proposed memristor has the following distinguishing features as compared to the other work presented in [2, 3, 4, 5, 6, 10, 17, 27, 28, 30, 32, 33, 34, 35, 36] : 1) less complexity. 2) can be on a chip integrated. 3) does not need any external device. 4) has a high number of resistor levels. The drain-to-source resistance of MOSFET (M1) represents the resistance of the memristor, which is changing by the voltage across the transistor M4. M4 is conecting as a capacitor by tying the drain, source, and bulk to Vss [26]. M2 and M3 transistors are the feedback circuit that controls the voltage across M4. The feedback circuit is controlled by external voltage sources (VA, VB).

Proposed emulator memristor circuit and its symbol.

3 Results

The proposed memristor is simulated using spectre simulator from Cadence. AMS 0.35 μm CMOS technology is used, and the power supply voltages of the circuit are Vdd = −Vss = 1.65V. The aspect ratios of the transistors are designed as (W/L)M1 = 30 μm/0.35 μm, (W/L)M2 = 3 μm/2 μm, (W/L)M3 = 2 μm/3 μm, and(W/L)M4 = 80 μm/60 μm. In order to draw the voltage-current characteristic of the proposed floating memristor, the sinusoidal signal has been applied to it, as shown in (Fig. 3).

The test circuit of the memristor characteristics.

The voltage-current characteristic of the proposed floating memristor for 2 MHz frequency is shown in (Fig. 4).

The voltage-current characteristics of memristor for 2 MHz.

The comparison of state of the art and this work are listed in (Tab. 1). The active and passive devices are recoded, operation frequency, emulator properties (floating or grounded) are listed in (Tab. 1).

Comparison of the proposed memristor circuit with previous works.

| Reference | Active component | Passive device | Frequency | Memristors type |

|---|---|---|---|---|

| [17] | 2 OP-AMPs, 1 Multiplier, 10 Transistors | 2 R, 1 C | 800 Hz | Grounded Memristor |

| [2] | CBTA, 1 Multiplier | 2 R, 1 C | 100 kHz | Grounded Memristor |

| [6] | 4 transistors | - | 100 MHz | Grounded Memristor |

| [10] | 4 transistors | - | 100 kHz | Grounded Memristor |

| [32] | 7 transistors | 1 C | 50 MHz | Grounded Memristor |

| [35] | VDCC, 2 transistors | 1 C | 2 MHz | Grounded Memristor |

| [34] | VDTA, single transistors | - | 50 MHz | Grounded Memristor |

| [28] | 3 OTA, 4 CCII | 6 R, 1 C | 10 kHz | Floating Memristor |

| [5] | 1 MO-OTA, 1 Multiplier | 1 R, 1 C | 1 kHz | Floating Memristor |

| [30] | 3 transistors | 1 C | 1 MHz | Floating Memristor |

| [36] | 1 CBTA | 2 C | 1 MHz | Floating Memristor |

| [4] | 1 OTA, 2 transistors | 1 C | 30 Hz | Floating Memristor |

| [3] | 10 transistors | 3 C | 5 Hz | Floating Memristor |

| [33] | 1 DDCC, 1 Multiplier | 2 R, 1 C | 1 MHz | Floating Memristor |

| [27] | 4 CCII, 1 Multiplier | 5 R, 1 C | 20.2 kHz | Floating Memristor |

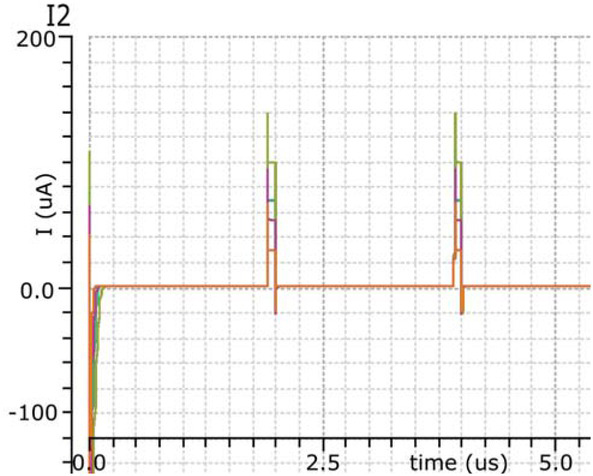

The proposed memristor can achieve up to 783 resistance levels with adaptation time equal to 500 ns between each level. The results show that the proposed memristor can be programmed up to 9.61-bit values which are higher than the recent memristors proposed in [7, 11, 13, 21, 22, 25] where authors programmed up to 121, 200, 64, 100, 30 and 24 levels, respectively. From the voltage-current characteristics of the memristor shown in (Fig. 4). Just like a biological synapse, the proposed memristor recovers the original state when the applied voltage is removed. Furthermore, the proposed memristors can be used as the weights of the synapses as well as to build the neuron for the memristor SNN as spiking adaptive sensor circuits. Moreover, the neurons built using this memristor do not need a reset after firing like the biological neurons. The proposed memristor with one transistor (1T1M) mimics synapse which can be programmed to 783 resistance levels using adapted pulses of 100 ns and controlling the transistor voltage gate to give more control of the memristor current as shown in (Fig. 5).

Memristor with transistor (1T1M) architecture used to program the memristor.

Monte-Carlo simulation of the 1T1M under temperature range (-40 °C to 85 °C) is given in (Fig. 6) to confirm workableness. The worst-case result is picked, as shown in (Fig. 7). In order to reset it the original weight of the synapse, the voltage of the gate transistor is adjusted, and the recovered result is shown in (Fig. 8).

Monte-Carlo simulation of the 1T1M in the temperature range (-40 °C to 85 °C).

Worst-case of the Monte-Carlo simulation for the 1T1M.

Recovered the worst-case of the Monte-Carlo simulation for the 1T1M.

The layout of the proposed floating memristor circuit (Fig. 9) in the figure which occupies 70 μm ∗ 85 μm chip area.

The layout of the proposed floating memristor emulator circuit.

4 Conclusions

In this work, a compact floating memristor circuit is presented, which consists of only four MOS-transistors without requiring any external devices. By comparing it with the previous designs that needed active components like a multiplier, OP-AMP, OTA, CBTA, VDCC, VDTA, DDCC, CCII, and passive elements like capacitor and resistor. The proposed floating memristor is implemented using AMS 0.35 μm CMOS technology and simulated with cadence design tools in the temperature range (-40 °C to 85 °C) and Monte-Carlo model. The proposed floating memristor is suitable for an adaptive synapse and in an adaptive spiking neuron.

References

[1] S. Alraho and A. König. Wide input range, fully-differential indirect current feedback instrumentation amplifier for self-x sensory systems/symmetrischer instrumentierungsverstärker mit indirekter stromgegenkopplung und hoher eingangsignalspanne für integrierte sensorsysteme mit self-x-eigenschaften. tm-Technisches Messen, 86(s1):62–66, 2019.10.1515/teme-2019-0054Search in Google Scholar

[2] U. E. Ayten, S. Minaei, and M. Sağbaş. Memristor emulator circuits using single cbta. AEU-IJEC, 82:109–118, 2017.10.1016/j.aeue.2017.08.008Search in Google Scholar

[3] Y. Babacan and F. Kaçar. Memristor emulator with spiketiming-dependent-plasticity. AEU-IJEC, 73:16–22, 2017.10.1016/j.aeue.2016.12.025Search in Google Scholar

[4] Y. Babacan and F. Kaçar. Floating memristor emulator with subthreshold region. AICSP, 90(2):471–475, 2017.10.1007/s10470-016-0888-9Search in Google Scholar

[5] Y. Babacan, A. Yesil, and F. Kacar. Memristor emulator with tunable characteristic and its experimental results. AEU-IJEC, 81:99–104, 2017.10.1016/j.aeue.2017.07.012Search in Google Scholar

[6] Y. Babacan, A. Yesil, and F. Gul. The fabrication and mosfet-only circuit implementation of semiconductor memristor. IEEE TED, 65(4):1625–1632, 2018.10.1109/TED.2018.2808530Search in Google Scholar

[7] J. Chen, W.-Q. Pan, Y. Li, R. Kuang, Y.-H. He, C.-Y. Lin, N. Duan, G.-R. Feng, H.-X. Zheng, T.-C. Chang, et al. Highprecision symmetric weight update of memristor by gate voltage ramping method for convolutional neural network accelerator. IEEE EDL, 41(3):353–356, 2020.10.1109/LED.2020.2968388Search in Google Scholar

[8] L. Chua. Memristor-the missing circuit element. IEEE Transactions on circuit theory, 18(5):507–519, 1971.10.1109/TCT.1971.1083337Search in Google Scholar

[9] T. Driscoll, J. Quinn, S. Klein, H.-T. Kim, B. Kim, Y. V. Pershin, M. Di Ventra, and D. Basov. Memristive adaptive filters. APL, 97(9):093502, 2010.10.1063/1.3485060Search in Google Scholar

[10] F. Gul. Circuit implementation of nano-scale tio 2 memristor using only metal-oxide-semiconductor transistors. IEEE EDL, 40(4):643–646, 2019.10.1109/LED.2019.2899889Search in Google Scholar

[11] I. Gupta, A. Serb, A. Khiat, R. Zeitler, S. Vassanelli, and T. Prodromakis. Real-time encoding and compression of neuronal spikes by metal-oxide memristors. Nature communications, 7(1):1–9, 2016.10.1038/ncomms12805Search in Google Scholar PubMed PubMed Central

[12] M. Gusev and S. Dustdar. Going back to the roots—the evolution of edge computing, an iot perspective. IEEE IC, 22 (2):5–15, 2018.10.1109/MIC.2018.022021657Search in Google Scholar

[13] H. Jiang, L. Han, P. Lin, Z. Wang, M. H. Jang, Q. Wu, M. Barnell, J. J. Yang, H. L. Xin, and Q. Xia. Sub-10 nm ta channel responsible for superior performance of a hfo 2 memristor. Scientific reports, 6:28525, 2016.10.1038/srep28525Search in Google Scholar PubMed PubMed Central

[14] A. C. Kammara and A. Koenig. Contributions to integrated adaptive spike coded sensor signal conditioning and digital conversion in neural architecture. In Sensors and Measuring Systems 2014; 17. ITG/GMA Symposium, pages 1–6. VDE, 2014.Search in Google Scholar

[15] A. C. Kammara and A. König. Increasing the resolution of an integrated adaptive spike coded sensor to digital conversion neuro-circuit by an enhanced place coding layer. In Symposium des AHMT, volume 9, page 2014, 2014.10.5162/AHMT2014/P5Search in Google Scholar

[16] A. Kammara S., Abhaya Chandra König. Robust adcs for dependable integrated measurement systems based on adaptive neuromorphic spiking realization. XXIX Messtechnisches Symposium, pages 157–164, 2015.10.1515/9783110408539-020Search in Google Scholar

[17] H. Kim, M. P. Sah, C. Yang, S. Cho, and L. O. Chua. Memristor emulator for memristor circuit applications. IEEE TCS, 59(10):2422–2431, 2012.10.1109/TCSI.2012.2188957Search in Google Scholar

[18] V. P. S. Kirar. Memristor: the missing circuit element and its application. International Journal of Electrical, Computer, Energetic, Electronic and Communication Engineering, 6: 1395–1397, 2012.Search in Google Scholar

[19] A. König et al. Ssdcα–inherently robust integrated biomimetic sensor-to-spike-to-digital converter based on peripheral neural ensembles. tm-Technisches Messen, 83(9): 531–542, 2016.10.1515/teme-2015-0119Search in Google Scholar

[20] O. Krestinskaya, A. P. James, and L. O. Chua. Neuromemristive circuits for edge computing: A review. IEEE TNNLS, 31 (1):4–23, 2020.10.1109/TNNLS.2019.2899262Search in Google Scholar PubMed

[21] C. Li, D. Belkin, Y. Li, P. Yan, M. Hu, N. Ge, H. Jiang, E. Montgomery, P. Lin, Z. Wang, et al. Efficient and self-adaptive in-situ learning in multilayer memristor neural networks. Nature communications, 9(1):1–8, 2018.10.1038/s41467-018-04484-2Search in Google Scholar PubMed PubMed Central

[22] E. J. Merced-Grafals, N. Dávila, N. Ge, R. S. Williams, and J. P. Strachan. Repeatable, accurate, and high speed multi-level programming of memristor 1t1r arrays for power efficient analog computing applications. Nanotechnology, 27 (36):365202, 2016.10.1088/0957-4484/27/36/365202Search in Google Scholar PubMed

[23] B. Muthuswamy. Implementing memristor based chaotic circuits. IJBC, 20(05):1335–1350, 2010.10.1142/S0218127410026514Search in Google Scholar

[24] Y. V. Pershin and M. Di Ventra. Practical approach to programmable analog circuits with memristors. IEEE TCSI, 57(8):1857–1864, 2010.10.1109/TCSI.2009.2038539Search in Google Scholar

[25] K. V. Pham, S. B. Tran, T. V. Nguyen, and K.-S. Min. Asymmetrical training scheme of binary-memristor-crossbar-based neural networks for energy-efficient edge-computing nanoscale systems. Micromachines, 10(2):141, 2019.10.3390/mi10020141Search in Google Scholar PubMed PubMed Central

[26] B. Razavi. Design of analog CMOS integrated circuits. Tata McGraw-Hill Education, 2017.Search in Google Scholar

[27] C. Sánchez-López, J. Mendoza-Lopez, M. Carrasco-Aguilar, and C. Muñiz-Montero. A floating analog memristor emulator circuit. IEEE Transactions on Circuits and Systems II: Express Briefs, 61(5):309–313, 2014.10.1109/TCSII.2014.2312806Search in Google Scholar

[28] H. Sözen and U. Çam. Electronically tunable memristor emulator circuit. AICSP, 89(3):655–663, 2016.10.1007/s10470-016-0785-2Search in Google Scholar

[29] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams. The missing memristor found. nature, 453(7191): 80–83, 2008.10.1038/nature06932Search in Google Scholar PubMed

[30] J. Vista and A. Ranjan. A simple floating mos-memristor for high-frequency applications. IEEE TVLSIS, 27(5):1186–1195, 2019.10.1109/TVLSI.2018.2890591Search in Google Scholar

[31] Q. Xia and J. J. Yang. Memristive crossbar arrays for brain-inspired computing. Nature materials, 18(4):309–323, 2019.10.1038/s41563-019-0291-xSearch in Google Scholar PubMed

[32] A. Yesil. A new grounded memristor emulator based on mosfet-c. AEU-International Journal of Electronics and Communications, 91:143–149, 2018.10.1016/j.aeue.2018.05.004Search in Google Scholar

[33] A. Yeşil, Y. Babacan, and F. Kaçar. A new ddcc based memristor emulator circuit and its applications. MJ, 45(3): 282–287, 2014.10.1016/j.mejo.2014.01.011Search in Google Scholar

[34] A. Yeşil, Y. Babacan, and F. Kaçar. Design and experimental evolution of memristor with only one vdta and one capacitor. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 38(6):1123–1132, 2018.10.1109/TCAD.2018.2834399Search in Google Scholar

[35] A. Yesil, Y. Babacan, and F. Kacar. Electronically tunable memristor based on vdcc. AEU-International Journal of Electronics and Communications, 107:282–290, 2019.10.1016/j.aeue.2019.05.038Search in Google Scholar

[36] A. Yesil, Y. Babacan, and F. Kacar. A new floating memristor based on cbta with grounded capacitors. JCSC, page 1950217, 2019.10.1142/S0218126619502177Search in Google Scholar

[37] Q. Zaman and A. König. Self-x integrated sensor circuits immune to measurement noise in the presence of input perturbation by using robust optimization/integrierte sensorelektronik mit self-x-eigenschaften und verbesserter immunität gegenüber rauscheinflüssen bei der messung und störung der eingangsgrößen durch ein robustes optimierungsverfahren. tm-Technisches Messen, 86(s1):107–111, 2019.10.1515/teme-2019-0053Search in Google Scholar

[38] Q. Zaman, S. Alraho, and A. König. Robust optimization of self-x sensory electronics in presences of environmental variations for industry 4 . 0. Sensor and Measurement Science International, pages 295–296, 2020.Search in Google Scholar

© 2020 Walter de Gruyter GmbH, Berlin/Boston

Articles in the same Issue

- Frontmatter

- Editorial

- XXXIV. Messtechnisches Symposium

- Beiträge

- Detektion der Auflagestege von Flachbett-Laserschneidmaschinen mittels Nahinfrarot-Beleuchtung

- Lichtfeld-Tiefenschätzung für die Vermessung teilspiegelnder Oberflächen

- Ganzheitliche Kalibrierung von Gewinden auf Basis eines dreidimensionalen Ansatzes

- Analyse von 3D-CT-Aufnahmen von Spänen zur Extrahierung der Segmentspanbildungsfrequenz

- Resolution enhancement through nearfield-assistance in interference microscopy

- Fertigung polymerer optischer Phasenplatten zur Erzeugung von Ringmoden mittels direkter Laserlithografie

- Direct-imaging DOEs for high-NA multi-spot confocal microscopy

- Methoden zur Minimierung des Rauscheinflusses durch Hitzeflimmern bei einem heterodynen Laser-Doppler-Vibrometer

- Inverse piezoelectric material parameter characterization using a single disc-shaped specimen

- Klassifikation von Grübchenschäden an Zahnrädern mittels Vibrationsmessungen

- Incorporation of phase information for improved time-dependent instrument recognition

- Akustische Zeitumkehrfokussierung in Wasser mittels FPGA-basierter Plattform

- De-Embedding-Ansatz zur Messung nichtidealer Kapazitäten mit kommerziellen Kapazitätssensoren

- Low-cost Indirect Measurement Methods for Self-x Integrated Sensory Electronics for Industry 4.0

- Reconfigurable Wide Input Range, Fully-Differential Indirect Current-Feedback Instrumentation Amplifier with Digital Offset Calibration for Self-X Measurement Systems

- A Compact Four Transistor CMOS-Design of a Floating Memristor for Adaptive Spiking Neural Networks and Corresponding Self-X Sensor Electronics to Industry 4.0

- Monte-Carlo-Methode zur Verringerung von Messfehlern bei der Materialparameterbestimmung mit Hohlraumresonatoren

- Bestimmung des Anregungsspektrums für kontaktlose breitbandige Messungen der Übertragungsfunktion mit Plasmaanregung und Laser-Doppler-Vibrometrie

- Self-sufficient vibration sensor for high voltage lines

- Flexibler organischer elektrochemischer Transistor als Biosensor für Organ-on-a-Chip

- Erkennung und Kompensation von Vergiftung durch Siloxane auf Halbleitergassensoren im temperaturzyklischen Betrieb

Articles in the same Issue

- Frontmatter

- Editorial

- XXXIV. Messtechnisches Symposium

- Beiträge

- Detektion der Auflagestege von Flachbett-Laserschneidmaschinen mittels Nahinfrarot-Beleuchtung

- Lichtfeld-Tiefenschätzung für die Vermessung teilspiegelnder Oberflächen

- Ganzheitliche Kalibrierung von Gewinden auf Basis eines dreidimensionalen Ansatzes

- Analyse von 3D-CT-Aufnahmen von Spänen zur Extrahierung der Segmentspanbildungsfrequenz

- Resolution enhancement through nearfield-assistance in interference microscopy

- Fertigung polymerer optischer Phasenplatten zur Erzeugung von Ringmoden mittels direkter Laserlithografie

- Direct-imaging DOEs for high-NA multi-spot confocal microscopy

- Methoden zur Minimierung des Rauscheinflusses durch Hitzeflimmern bei einem heterodynen Laser-Doppler-Vibrometer

- Inverse piezoelectric material parameter characterization using a single disc-shaped specimen

- Klassifikation von Grübchenschäden an Zahnrädern mittels Vibrationsmessungen

- Incorporation of phase information for improved time-dependent instrument recognition

- Akustische Zeitumkehrfokussierung in Wasser mittels FPGA-basierter Plattform

- De-Embedding-Ansatz zur Messung nichtidealer Kapazitäten mit kommerziellen Kapazitätssensoren

- Low-cost Indirect Measurement Methods for Self-x Integrated Sensory Electronics for Industry 4.0

- Reconfigurable Wide Input Range, Fully-Differential Indirect Current-Feedback Instrumentation Amplifier with Digital Offset Calibration for Self-X Measurement Systems

- A Compact Four Transistor CMOS-Design of a Floating Memristor for Adaptive Spiking Neural Networks and Corresponding Self-X Sensor Electronics to Industry 4.0

- Monte-Carlo-Methode zur Verringerung von Messfehlern bei der Materialparameterbestimmung mit Hohlraumresonatoren

- Bestimmung des Anregungsspektrums für kontaktlose breitbandige Messungen der Übertragungsfunktion mit Plasmaanregung und Laser-Doppler-Vibrometrie

- Self-sufficient vibration sensor for high voltage lines

- Flexibler organischer elektrochemischer Transistor als Biosensor für Organ-on-a-Chip

- Erkennung und Kompensation von Vergiftung durch Siloxane auf Halbleitergassensoren im temperaturzyklischen Betrieb