### A. Antworten zu den Aufgaben

**Aufgabe 1** Was ist ein Computer?

Ein Computer ist ein universell programmierbarer Rechner, mit dem sich unterschiedlichste Aufgaben lösen lassen.

Aufgabe 2 Wie hieß der erste Computer?

Je nach Sichtweise wird der Zuse Z3 (1941) oder der ENIAC (1944) als erster Computer angesehen.

**Aufgabe 3** Forschen Sie nach, warum der Z1 üblicherweise noch nicht als Computer gilt.

Der Z1 arbeitete mechanisch und hatte ein Problem mit der Zuverlässigkeit: Es verhakte sich konstruktionsbedingt die Mechanik, so dass er nicht wirklich funktionsfähig war.

Aufgabe 4 Vergleichen Sie genannten Beispiele nach Preis, Hauptspeicher- und Festplattenausstattung mit heutigen Angeboten! Um welchen Faktor unterscheiden sich die genannten Größen? Wie groß ist demnach der Verdoppelungszeitraum aus dem MOOREschen Gesetz?

Es ist schwer abzuschätzen, welche Parameter ein "typischer" PC mitbringt: Zu groß ist die Bandbreite dessen, was aktuell angeboten wird und auch, was man zu einem bestimmten Preis bekommt. Daher kann es sich nachfolgend nur um grobe Schätzungen handeln, die stark variieren können. Ebenso sind Angaben von Nachkommastellen sehr differenziert zu betrachten.

Es gilt für den Faktor f, um den sich eine Größe im betrachteten Zeitraum verbessert hat:

Faktor f = Wert(2016)/Wert(1983)

Anzahl v der Verdopplungen im betrachteten Zeitraum:

v = ld f = ln f/ln 2, wobei ld der Logarithmus zur Basis 2 ist (Logarithmus Dualis).

Der Verdopplungszeitraum (Zeitraum, den *eine* Verdopplung benötigt) ergibt sich aus der gesamten Zeitspanne von T=33 Jahren (von Mitte 1983 bis Mitte 2016 gerechnet) und der Anzahl der Verdopplungen währenddessen:

t = T/|v|

Beim Preis ergibt sich keine Zunahme, sondern Abnahme. Das resultiert in einem negativen Vorzeichen bei v, das aber beim Berechnen des Verdopplungszeitraums ignoriert wird. Deswegen verwenden wir dafür den Betrag von v.

Bei typischen "Informatik"-Größen, z.B. Speichergrößen, nimmt man Zweierpotenzen anstelle der Zehnerpotenzen. So ist 1 kByte nicht 1000 Bytes, sondern 1024 Bytes. Das wurde bei den entsprechenden Zahlenwerten in der Tabelle berücksichtigt.

Wir führen noch einige zusätzliche Schätzungen durch. Betrachtet man die Rechenleistung R, dann kann man diese ungefähr als Produkt

R = Anzahl Prozessorkerne · Wortbreite · Taktfrequenz · Optimierungsfaktor

abschätzen. Bei dieser Schätzung ist berücksichtigt, dass die interne Architektur im Laufe der Jahre erheblich optimiert wurde, was die Rechenleistung zusätzlich anwachsen ließ. So benötigen z.B. manche Befehle, die früher mehrere Takte brauchten, nur noch einen Takt. Auch können heutige Prozessoren in jedem Prozessorkern mehrere Operationen gleichzeitig ausführen. Der Optimierungsfaktor wurde eher konservativ als 10 angenommen.

|                      | 1983      | 2016       | Faktor f  | V     | t [Jahre] bzw.<br>[Monate] |

|----------------------|-----------|------------|-----------|-------|----------------------------|

| Anzahl Prozessor-    | 1         | 8          | 8         | 3     | 11 Jahre                   |

| kerne                |           |            |           |       |                            |

| Wortbreite           | 16 Bit    | 64 Bit     | 4         | 2     | 16 Jahre                   |

| Taktfrequenz         | 4,77 MHz  | 3,5 GHz    | 734       | 9,52  | 3,47 Jahre                 |

| Hauptspeicher        | 256 kB    | 8 GB       | 32.768    | 15    | 2,20 Jahre                 |

| Festplatte           | 10 MB     | 3 TB       | 349.525   | 18,4  | 1,79 Jahre                 |

| Preis                | 30.000 DM | 1.000 Euro | 1/15      | -3,91 | 8,43 Jahre                 |

| Rechenleistung       |           |            | 96.000    | 16,55 | 1,99 Jahre                 |

| Rechenleistung/Preis |           |            | 1.440.000 | 20,46 | 1,61 Jahre                 |

Tab. A.1: Zunahme der Leistungsfähigkeit von Computern

Man erkennt, dass der Verdopplungszeitraum stark von der betrachteten Größe abhängt. In der Literatur findet man Zeiträume von 18 bis 24 Monaten für eine Verdopplung, also 1,5 bis 2 Jahre. Das kann durch unsere Schätzung für Festplatten und Rechenleistung sowie für Rechenleistung/Preis bestätigt werden.

Allerdings sollte man berücksichtigen, dass manche Größen derzeit an Grenzen stoßen, z.B. die Festplattengröße, die in den vergangenen Jahren deutlich langsamer angestiegen ist als zuvor. Ferner ist sowohl bei der Taktfrequenz als auch beim Preis für einen gut ausgestatteten PC eine gewisse Stabilisierung eingetreten, so dass eine Näherung durch eine Exponentialkurve nicht mehr angemessen scheint.

Aufgabe 5 Finden Sie heraus, welche Arten von PCs derzeit auf dem Markt beworben werden und wie sie sich unterscheiden!

#### Eine Auswahl:

- Desktop-PC: Der "klassische" PC mit Tower-, Midi-Tower, und anderen Gehäusen

- Workstation: Ein besonders leistungsfähiger PC. Der Begriff ist auch bei High-End-Notebooks zu finden.

- Notebook (Laptop): Tragbarer Rechner mit Akku und eingebautem Flachbildschirm

- Netbook: besonders handlicher, billiger Notebook-ähnlicher Rechner mit geringer Ausstattung und Rechenleistung

- Tablet PC: Notebook-ähnlicher Rechner mit Touch Screen, der per Berührung oder Stifteingabe bedient wird. Eine Tastatur kann physisch vorhanden sein, oder sie wird als virtuelle Tastatur auf dem Bildschirm abgebildet.

- Aufgabe 6 Schrauben Sie einen PC auf und sehen Sie nach, welche Komponenten eingebaut sind und wie sie miteinander verbunden sind! (Für etwaige Garantieverluste wird keine Gewähr übernommen ...)

Diese Aufgabe müssen Sie schon selber lösen ...

Aufgabe 7 Informieren Sie sich über das Aussehen eines Serverraumes. Wenn möglich, besichtigen Sie einen. Welche Geräte und Vorrichtungen finden sich außer den Servern typischerweise noch darin? Wie wird die Datensicherung (Erstellung von Sicherheitskopien) durchgeführt?

Man findet dort z.B. auch noch

- Speichermedien wie SAN

- Netzwerkkomponenten wie Switches, Router, Firewall

- Netzwerkanbindungen wie Netzwerk-Backbone, Glasfaser nach draußen

- Geräte zur Datensicherung wie Tape Library: In dieser befindet sich eine Menge von Backup-Bändern, die von der Library eigenständig verwaltet wird. In gewissen Zeitabständen werden die Bänder mit neuen Daten überschrieben, verschlissene Bänder werden ausgesondert.

- Tresor für Backup-Medien; dieser sollte idealerweise in einem anderen Raum stehen

- Brand- und Wassermeldesensoren

- Feuerlöscher oder Löschanlage

- Alarmanlage

#### **Aufgabe 8** Welche Hauptvorteile von Mainframes vermuten Sie?

Der Client bzw. das Terminal, an dem der Benutzer arbeitet, braucht keine leistungsfähige Hardware zu besitzen. Häufig reicht bereits, wenn es ein vom Mainframe geliefertes Bild darstellen und Benutzereingaben an den Mainframe weiterleiten kann. Festplatten und optische Laufwerke sind nicht immer vorhanden. Das führt zu geringen Kosten und geringem Verwaltungsaufwand pro Benutzer. Datenspeicherung und somit auch Datensicherung kön-

nen sehr gut zentral erfolgen. Sensible Informationen können in besonders geschützten Räumen untergebracht werden.

Aufgabe 9 Welche Art von Clients eignet sich besonders gut in Verbindung mit Mainframes?

Thin Clients eignen sich besonders gut, siehe auch Frage 8.

Aufgabe 10 Informieren Sie sich auf http://www.top500.org/ über die derzeit schnellsten Supercomputer. Welche Rechenleistung haben sie? Welche Informationen lassen sich zu Hauptspeicher, Anzahl der Prozessorkerne und Betriebssystem finden?

Gemäß Liste vom Juni 2016 war der schnellste Rechner der chinesische Sunway TaihuLight, der im National Supercomputing Center in Wuxi steht. Seine Rechenleistung beträgt 93 Petaflop/s beim Linpack Benchmark. Er verfügt über 40.960 Knoten mit je 260 Kernen, was insgesamt 10.649.600 Kerne ergibt. In der derzeitigen Ausbaustufe besitzt er 1,31 Petabyte RAM. Betriebssystem ist Sunway RaiseOS 2.0.5, eine Linux-Variante.

Die nötige elektrische Leistung beträgt 15,37 MW. Die Anschaffungskosten werden mit umgerechnet 273 Millionen US-Dollar angegeben. Der Computer wird u.a. eingesetzt zur Erdölsuche, für Life Sciences und zur Wettervorhersage.

Gemäß Sublistengenerator auf der Website werden sämtliche der 500 schnellsten Rechner mit Unixoiden Betriebssystemen (u.a. Linux, Unix) betrieben. Dabei entfallen 497 auf Linux, die restlichen 3 auf Unix. Windows und andere Betriebssysteme sind dort nicht vertreten.

Aufgabe 11 Finden Sie 10 Embedded Systems in Ihrem Zuhause und in Ihrer unmittelbaren Umgebung. Sammeln Sie so viele Informationen wie möglich darüber (Zweck, Typ des Mikrocontrollers, Speichergröße, etc.)

Z.B. EC-Karte, Mensa-Karte, Mitarbeiterausweis, elektronischer Personalausweis und Reisepass, Handy, Waschmaschine, DVD-Player, Fernseher, Festplattenrecorder, PC-Tastatur, Soundkarte im PC, etc. Die weiteren Informationen sind stark von der Art des Mikrocontrollers abhängig, z.B. 8-Bit-Mikrocontroller auf 8051-Basis und 16 KB RAM, 32 kB ROM und 64 kB Flash-Speicher.

**Aufgabe 12** Welche Grundvoraussetzung müssen die Adressen erfüllen, die von Speicher- und E/A-Bausteinen belegt werden?

Sie müssen eindeutig sein und dürfen sich nicht überschneiden. Einige Prozessoren verfügen allerdings über einen "Umschalter" zwischen Speicher- und E/A-Bereich, der doch erlaubt, dass beide dieselben Adressen belegen.

Zusammenhängend brauchen die Adressbereiche nicht notwendigerweise zu sein. Es gibt bei vielen Rechnern unbelegte Adressen, die keinem Baustein zugeordnet sind. Das ist der Fall, wenn nicht die maximal mögliche Zahl von Speicher- und E/A-Bausteinen vorhanden ist.

Aufgabe 13 Bei jeder Adresse fühlt sich MAXIMAL ein Baustein angesprochen. Unter welchen Gegebenheiten könnte es vorkommen, dass GAR KEINER angesprochen wird? Was könnte in so einem Fall passieren? Wie lässt es sich vermeiden?

Nicht zu jedem Zeitpunkt wird vom Prozessor ein Speicher- oder E/A-Baustein angesprochen. Daher kommt es sehr häufig vor, dass kein Baustein ausgewählt wird. Hier ist allerdings eher gemeint, dass der Prozessor Daten von einer Adresse lesen oder dorthin schreiben will, diese Adresse aber keinem Baustein zugeordnet ist.

Ein Lese- oder Schreibvorgang würde also entweder ignoriert werden oder er würde eine Fehlermeldung ("Speicherzugriffsverletzung") hervorrufen.

Das Ansprechen nicht vorhandener Adressen könnte z.B. ein Programmierfehler sein. Der Programmierer sollte also sorgfältig Grenzen von Arrays beachten und nicht z.B. i[5] ansprechen, wenn es nur maximal i[4] gibt.

**Aufgabe 14** Welchen Einfluss der Wortbreite auf die Geschwindigkeit des Computers vermuten Sie?

Wenn man die Wortbreite verdoppelt, können in einem Zyklus doppelt so viele Daten übertragen werden wie zuvor. Die Performance des Computer erhöht sich also deutlich.

Weil man nicht immer die volle Wortbreite benötigt und nicht ununterbrochen Daten über den Bus schickt, wird sich die Performance aber weniger als verdoppeln.

Aufgabe 15 Welchen Vorteil könnte es haben, wenn Befehle auf Vorrat in den Predecode Cache geholt werden? Unter welchen Umständen bringt es nichts?

Im Predecode Cache wird eine vordecodierte Form der Befehle abgelegt. Das erspart erneutes Holen und Decodieren, wenn Befehle mehrfach ausgeführt werden, z.B. bei Programmschleifen.

Wenn Befehle nicht mehrfach benötigt werden, bringt der Predecode Cache keinen Vorteil.

**Aufgabe 16** Ein PC habe einen Vierkernprozessor. Wie ist er nach der FLYNNschen Taxonomie zu klassifizieren?

Jeder Kern kann unabhängig von den anderen Befehle abarbeiten. Zu einem gegebenen Zeitpunkt werden also mehrere Befehle (MI) ausgeführt, jeder mit unterschiedlichen Daten (MD). Der Vierkernprozessor fällt also in die Kategorie MIMD.

# **Aufgabe 17** In welche Klasse der FLYNNschen Taxonomie fällt ein moderner Grafikprozessor?

Eine typische Anwendung von Grafikprozessoren ist die gleichzeitige Bearbeitung zahlreicher Teile eines Bildes (MD). Dazu ist eine zentrale Steuerung (SI) sinnvoll, weil jeder Teil auf dieselbe Weise bearbeitet wird, z.B. um Kanten zu extrahieren oder eine Filterung durchzuführen. Es handelt sich dabei somit um eine SIMD-Architektur. Sie ist nach wie vor weit verbreitet und besitzt den Vorteil eines relativ einfachen und kostengünstigen Aufbaus.

Immer häufiger werden Grafikprozessoren aber für universellere Aufgaben eingesetzt, z.B. für wissenschaftliche Berechnungen und das Lösen von Gleichungssystemen. Daher ist ein Trend zu MIMD zu beobachten, wobei die Grafikkerne zwar gleichartige Operationen durchführen, also dasselbe Programm abarbeiten. Das erfolgt aber nicht mehr unter streng zentraler Kontrolle, sondern jeder Kern kann zu einem gegebenen Zeitpunkt an einer anderen Stelle des Programmes sein. Dafür wurde der Begriff *SPMD* (single program, multiple data) geprägt. SPMD ist ein Spezialfall von MIMD.

#### **Aufgabe 18** Wie stellt man Multiprozessorsysteme im ECS dar?

Multiprozessorsysteme haben mehrere Prozessoren, somit auch mehrere Steuerwerke und mehrere Rechenwerke. Davon unabhängig ist die Wortbreite. Beim Tripel (k, d, w) sind also k und d jeweils größer 1.

#### **Aufgabe 19** Wie stellt man Feldrechner im ECS dar?

Ein Feldrechner zeichnet sich dadurch aus, dass ein Feld von Verarbeitungselementen, also Rechenwerken, zentral gesteuert wird. Es gilt also k=1, d>1.

**Aufgabe 20** Woran könnte es liegen, dass zahlreiche Benchmark-Programme keine Grafik- und E/A-Befehle messen?

Grafik und E/A befinden sich außerhalb der CPU. Ein Benchmark-Programm, das die CPU-Leistung misst, wird diese Bereiche also unberücksichtigt lassen.

Benchmark-Programme, die das gesamte System einbeziehen, ermitteln Grafikleistung und E/A-Leistung häufig als separate Werte.

Aufgabe 21 Warum ist eine statische Einteilung der Computer nach Rechenleistung nicht sinnvoll? Z.B. "Ab Rechenleistung x handelt es sich um einen Supercomputer".

Die Rechenleistung ist eine sich äußerst dynamisch ändernde Größe. Ein Supercomputer, der zu den weltschnellsten zählt, kommt einige Jahre später womöglich nicht einmal mehr unter die Top 500. Für solche dynamischen Größen ist eine Angabe statischer Größen wenig sinnvoll. Besser sind "mitwachsende" Definitionen, die z.B. einen Supercomputer in Relation zu Nicht-Supercomputern setzen.

Aufgabe 22 In den Medien wird von einem Supercomputer berichtet, der z.B. 25 PFLOPS (PetaFLOPS) schnell ist. Wieviele MFLOPS sind das?

25 PFLOPS =  $25 \cdot 10^{15}$  FLOPS =  $25 \cdot 10^{15}/10^6$  MFLOPS =  $25 \cdot 10^9$  MFLOPS =  $25 \cdot 000 \cdot 000 \cdot 000$  MFLOPS

Aufgabe 23 Wie lange braucht der 25 PFLOPS-Supercomputer für eine Berechnung, die bei 1 MFLOPS Rechenleistung 10 Jahre dauert?

$T = 10 [a]/(25 \cdot 10^9) = 10 \cdot 365 \cdot 24 \cdot 60 \cdot 60 [s]/(25 \cdot 10^9) = 0.0126144 [s] = 12,6144 [ms]$ Oder mit anderen Worten: Der Supercomputer könnte jede Sekunde 79 solche Berechnungen durchführen, die bei dem Beispielcomputer jeweils 10 Jahre dauern würden.

Aufgabe 24 Führt Caching in jedem Falle zu einem schnelleren Zugriff auf Speicherstellen oder sind auch Fälle denkbar, wo Zugriffe langsamer als ohne Caching erfolgen?

Das Caching an sich benötigt etwas Zeit: Der Cache-Controller muss nachsehen, ob sich die Daten bereits im Cache befinden. Das wäre ohne Caching nicht nötig.

Andererseits bringt das Caching keinen Nutzen, wenn Daten nur ein einziges Mal benötigt werden. In diesem Fall bleibt also nur der Nachteil des höheren Zeitaufwandes, so dass die Zugriffe ohne Caching schneller erfolgen würden.

Aufgabe 25 Für den Cache benötigt man ohnehin schnellen Speicher. Was könnte der Grund dafür sein, dass man nicht den gesamten Hauptspeicher aus diesen Bausteinen aufbaut? Dann bräuchte man kein Caching.

Cache für den Hauptspeicher ist üblicherweise aus sehr schnellem und damit auch extrem teurem statischen RAM aufgebaut. Neben dem Preisnachteil ist statisches RAM auch nicht so hoch integrierbar wie das für den Hauptspeicher eingesetzte dynamische RAM. Weil man den Cache viel kleiner als den Hauptspeicher wählt, bekommt man einen guten Kompromiss aus Mehrkosten und Nutzen.

**Aufgabe 26** Welche Auswirkung der Cache-Größe auf die Performance ist zu erwarten?

Je größer der Cache, desto mehr Code bzw. Daten profitieren vom Caching. Der Zusammenhang ist allerdings nicht proportional, sondern eher exponentiell. Die ersten paar Kilobytes Cache bringen am meisten, denn Schleifen, die häufig durchlaufen werden, sind meist nicht besonders groß und passen idealerweise vollständig in den Cache. Ähnliches gilt für die am meisten verwendeten Datenstrukturen. Man kann mit wenigen Kilobytes Cache schon recht hohe Trefferraten und somit eine gute Performanceverbesserung erzielen.

Um die Performance spürbar weiter zu verbessern, muss man den Cache-Speicher z.B. verdoppeln oder vervierfachen. Jede weitere Performancesteigerung benötigt um ein Mehrfaches größeren Cache.

## Aufgabe 27 Durch welche Art von Ereignis könnte das Zurückschreiben der Daten in den Hauptspeicher ausgelöst werden?

Das Zurückschreiben erfolgt, sobald die Cache Line anderweitig benötigt wird. Das könnte z.B. der Fall sein, wenn neue Anwendungen gestartet werden oder bisher nicht verwendete Bereiche einer Anwendung durchlaufen werden. Auch das Öffnen einer Datei, aus der größere Datenmengen gelesen und im Cache zwischengespeichert werden, könnte das Zurückschreiben auslösen

### Aufgabe 28 Was könnte passieren, wenn man den Hauptspeicher aufrüstet, um einen Rechner schneller zu machen?

Falls man mehr Hauptspeicher einbaut als das Cacheable Area umfasst, dann wird ein Teil des Hauptspeichers nicht mehr vom Caching profitieren. Es kann sein, dass ein Teil des Betriebssystems oder anderer Code bzw. Daten, die häufig benötigt werden, in diesen langsamen Teil des Hauptspeichers gelangen und somit den Rechner herunterbremsen.

Die Problematik wird dadurch verschärft, dass Betriebssysteme dazu neigen, den gesamten Hauptspeicher mit Code oder Daten zu belegen. Der Hauptspeicher ist nämlich deutlich schneller als eine Festplatte, und wenn Daten schon im Hauptspeicher stehen und nicht erst von der Festplatte geladen werden müssen, geht das erheblich schneller. So wird der Hauptspeicher teilweise "vorsorglich" mit Daten gefüllt, für den Fall dass man diese einmal brauchen sollte. Dabei wird kein Unterschied zwischen dem Bereich innerhalb und außerhalb des Cacheable Area gemacht.

Anmerkung: Unabhängig vom Caching kann ein Prozessor im 32-Bit-Modus nur maximal 4 GByte ansprechen, von denen je nach Betriebssystem z.B. nur 3 GByte genutzt werden können. Baut man mehr Hauptspeicher ein, verwendet aber kein 64-Bit-Betriebssystem, dann hat man keinen Vorteil von dem über diese Grenzen hinausgehenden Hauptspeicher.

### **Aufgabe 29** Warum kann man die Cache-Inhalte im Gegensatz zu Büchern einfach wegwerfen?

Bücher hat man üblicherweise nur einmal zur Verfügung und man wird sich nicht jedes Mal eine Kopie davon machen, wenn man es aus dem Regal holt. Somit existiert nur das Original, das seinen Ort wechselt.

Im Cache wird dagegen jeweils eine Kopie des Originals angelegt. Somit kann man die Kopie problemlos löschen, wenn man sie nicht mehr benötigt, denn das Original bleibt an der ursprünglichen Stelle erhalten.

#### **Aufgabe 30** Welchen Einfluss hat die Pipelinelänge auf die Performance? (beispielhaft)

Hat die Pipeline nur wenige Stufen, dann werden nur wenige Anweisungen parallel abgearbeitet. Die Parallelisierung ist somit gering, der Nutzen ebenfalls.

Ist die Pipeline sehr lang, dann benötigt man sehr viele passende Operationen hintereinander, damit die Pipeline nicht leerläuft bzw. das Risiko des Leerlaufens steigt mit der Pipelinelänge.

Eine optimale Pipeline darf somit weder zu kurz noch zu lang sein. Für viele Zwecke ist eine Pipelinelänge von 8 bis 9 Stufen angemessen.

Aufgabe 31 Alles in allem scheint die Harvard-Architektur das bessere Konzept zu sein. Was mögen Gründe sein, warum die VON-NEUMANN-ARCHITEKTUR im PC-Bereich trotzdem eine so dominierende Rolle besitzt?

Ein wesentlicher Grund ist, dass PCs von je her eine VON-NEUMANN-ARCHITEKTUR besitzen. Die gesamte Software, sowohl Betriebssysteme als auch Anwendungen, sind darauf ausgelegt. Ein grundlegender Architekturwechsel würde es erfordern, auch die Software grundlegend zu überarbeiten. Das würde immense Kosten verursachen.

**Aufgabe 32** Welchen Unterschied macht es, ob man von einem UND-Gatter oder von einer UND-Verknüpfung redet?

Die UND-Verknüpfung ist eine Operation der BOOLEschen Algebra, die mit Nullen und Einsen arbeitet und ein abstraktes Denkmodell ist. Dagegen ist das UND-Gatter ein Stück Hardware, das die UND-Verknüpfung umsetzt.

UND-Gatter können je nach verwendeter Repräsentation von Nullen und Einsen sowie abhängig von der Technologie ganz unterschiedlich aufgebaut sein. Dagegen funktioniert eine UND-Verknüpfung im Sinne der BOOLEschen Algebra immer auf dieselbe Weise.

**Aufgabe 33** Geben Sie die Wahrheitstabelle eines NAND-Gatters mit drei Eingängen an!

Tab. A.2: Wahrheitstabelle eines NAND-Gatters mit drei Eingängen

| X <sub>2</sub> | $\mathbf{x}_1$ | $x_0$ | y |

|----------------|----------------|-------|---|

| 0              | 0              | 0     | 1 |

| 0              | 0              | 1     | 1 |

| 0              | 1              | 0     | 1 |

| 0              | 1              | 1     | 1 |

| 1              | 0              | 0     | 1 |

| 1              | 0              | 1     | 1 |

| 1              | 1              | 0     | 1 |

| 1              | 1              | 1     | 0 |

Aufgabe 34 Geben Sie die Wahrheitstabelle eines UND-Gatters mit zwei Eingängen an, bei dem der Eingang x<sub>1</sub> invertiert ist!

Tab. A.3: Wahrheitstabelle eines UND-Gatters mit zwei Eingängen und invertiertem x1

| $\mathbf{x}_1$ | $x_0$ | $\neg_{X_1}$ | $y=(\neg x_1)x_0$ |

|----------------|-------|--------------|-------------------|

| 0              | 0     | 1            | 0                 |

| 0              | 1     | 1            | 1                 |

| 1              | 0     | 0            | 0                 |

| 1              | 1     | 0            | 0                 |

Wie man sieht, unterscheidet sich die Spalte y von der der NAND-Verknüpfung. Es spielt also eine Rolle, ob man am Ausgang oder an einem Eingang invertiert.

**Aufgabe 35** Geben Sie die Wahrheitstabelle eines Multiplexers 4:1 an!

Tab. A.4: Wahrheitstabelle eines Multiplexers 4:1

| $s_1$ | $s_0$ | у              |

|-------|-------|----------------|

| 0     | 0     | $x_0$          |

| 0     | 1     | $\mathbf{x}_1$ |

| 1     | 0     | $\mathbf{x}_2$ |

| 1     | 1     | X3             |

Der Multiplexer benötigt zwei Steuersignale  $s_0$  und  $s_1$ , um damit einen von  $4 = 2^2$  Eingängen  $x_0 \dots x_3$  auswählen zu können. Der ausgewählte Eingang wird zum Ausgang y durchgeschaltet, dieser nimmt also den Wert des Eingangs an.

| Aufgabe 36 | Beschalten Sie einen 8:1-Multiplexer so, dass folgende Wahrheitstabelle |

|------------|-------------------------------------------------------------------------|

|            | implementiert wird:                                                     |

| $\mathbf{x}_2$ | $\mathbf{x}_1$ | $x_0$ | y |

|----------------|----------------|-------|---|

| 0              | 0              | 0     | 1 |

| 0              | 0              | 1     | 1 |

| 0              | 1              | 0     | 1 |

| 0              | 1              | 1     | 0 |

| 1              | 0              | 0     | 1 |

| 1              | 0              | 1     | 0 |

| 1              | 1              | 0     | 1 |

| 1              | 1              | 1     | 1 |

**Hinweis:** "Beschalten" heißt, dass an vorhandene Eingänge eine feste 0 oder feste 1 angelegt wird, dass Ein- und Ausgänge mit Formelbuchstaben aus der Aufgabenstellung versehen werden und – falls erlaubt – dass Gatter an die Ein- und Ausgänge geschaltet werden. Eine Änderung am internen Aufbau eines vorgegebenen Bausteins ist nicht gestattet.

Abb. A.1: Beschaltung eines MUX 8:1 zur Umsetzung einer Wahrheitstabelle

In einer Zeile n der Wahrheitstabelle soll am Ausgang y ein bestimmter Wert erscheinen. Legt man diesen Wert an den Eingang  $e_n$  des Multiplexers, dann wird dieser zum Ausgang y durchgeschaltet, wenn die Steuersignale  $x_0 \dots x_2$  den Wert n als Dualzahl annehmen. Wir können also mit  $x_0 \dots x_2$  jeden Wert der Wahrheitstabelle an y erzeugen.

Aufgahe 37

| Aufgabe   | Geben Sie die Wahrhei               | tstabelle eines Demultiplexers 1:4 an! |

|-----------|-------------------------------------|----------------------------------------|

| Tab. A.5: | Wahrheitstabelle eines Demultiplexe | rs 1:4                                 |

| $s_1$ | $s_0$ | <b>y</b> <sub>0</sub> | y <sub>1</sub> | <b>y</b> <sub>2</sub> | <b>y</b> <sub>3</sub> |

|-------|-------|-----------------------|----------------|-----------------------|-----------------------|

| 0     | 0     | X                     | 0              | 0                     | 0                     |

| 0     | 1     | 0                     | X              | 0                     | 0                     |

| 1     | 0     | 0                     | 0              | X                     | 0                     |

| 1     | 1     | 0                     | 0              | 0                     | X                     |

Der Eingang x wird zu demjenigen Ausgang yi weitergeleitet, dessen Nummer i mittels s<sub>1</sub> und so als Dualzahl ausgewählt wurde.

Aufgabe 38 Beschalten Sie einen 1:8-Demultiplexer so, dass er als 2-Bit-Adressdecoder arbeitet.

Abb. A.2: DMUX 1:8

In Abb. A.2 ist das Schaltzeichen des unbeschalteten DMUX 1:8 zu sehen. Es sind zwei Teilaufgaben zu lösen:

- Aus dem Demultiplexer soll ein Adressdecoder gemacht werden. Ein Adressdecoder legt einen ausgewählten Ausgang auf 1, während ein Demultiplexer einen Eingang e dorthin durchschaltet. Legen wir beim Demultiplexer somit e auf 1, haben wir dieselbe Arbeitsweise wie beim Adressdecoder.

- Der 1:8-Demultiplexer arbeitet mit 3 Steuersignalen, der 2-Bit-Adressdecoder nur mit zweien.

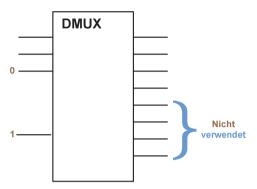

Wir nutzen also nur den halben Demultiplexer und lassen die andere Hälfte "brach liegen". Wir können dazu so dauerhaft auf 0 legen oder dauerhaft auf 1 legen. Aber genauso gut könnte man das mit s<sub>1</sub> oder s<sub>2</sub> machen. Daher gibt es sechs mögliche Lösungen. Eine davon ist in Abb. A.3 zu sehen.

Abb. A.3: Beschaltung eines DMUX 1:8

Wenn man  $s_2$  konstant auf 0 legt, kann  $(s_2s_1s_0)_2$  nur noch Werte von  $(000)_2$  bis  $(011)_2$  annehmen. Es können also nur noch die Ausgänge  $y_0$  bis  $y_3$  selektiert werden.  $y_4$  bis  $y_7$  liegen somit brach.

#### **Aufgabe 39** Wie könnte man mit weniger Steuersignalen auskommen?

Man könnte beispielsweise beim Sender und Empfänger die momentane Position speichern und mit einem einzigen Steuersignal einen Zähltakt übertragen, sobald auf den nächsthöheren Kanal geschaltet werden soll.

Nachteilig daran ist, dass man Sender und Empfänger dennoch synchronisieren können muss, damit z.B. beim Verbindungsaufbau beide mit demselben Kanal beginnen. Auch kann man die Kanäle auf diese Weise nur in einer festgelegten Reihenfolge durchschalten und nicht mehr beliebig.

**Aufgabe 40** Wie viele Leitungen benötigt man mit dem beschriebenen Verfahren zur Übertragung von 128 Kanälen?

Es sind 1 + 1d 128 = 1 + 7 = 8 Leitungen erforderlich.

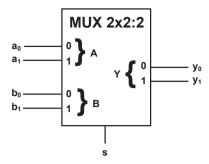

Aufgabe 41 Skizzieren Sie die Schaltung eines 2 × 2:2-Multiplexers, der aus 2:1-Multiplexern zu bilden ist. Geben Sie das Schaltzeichen an.

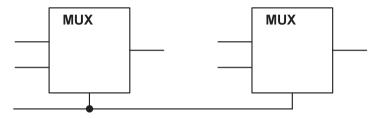

Ein Multiplexer 2 × 2:2 hat zwei Eingangsbündel A und B, die jeweils aus 2 Signalen bestehen. Eines davon wird ausgewählt und zum Ausgang weitergeleitet, der somit ebenfalls ein Bündel aus 2 Signalen sein muss.

Um eines von 2 Bündeln auszuwählen, genügt ein einziges Steuersignal, da  $2^1 = 2$ . Somit kommt man auf folgendes Schaltzeichen:

Abb. A.4: MUX 2 × 2:2

Möchte man diesen Multiplexer aus 2:1-Multiplexern bilden, dann muss man diese mit einem gemeinsamen s versehen, weil das Steuersignal nun nicht nur eines sondern 2 Datensignale gleichzeitig zum Ausgang weiterleiten soll:

Abb. A.5: MUX 2 × 2:2 aus MUX 2:1

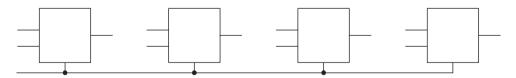

#### **Aufgabe 42** Bilden Sie einen Multiplexer $2 \times 4:4$ aus 2:1-Multiplexern.

Man geht hier genauso wie bei der vorigen Aufgabe vor, nur dass man jetzt Bündel mit 4 Signalen hat und somit noch zwei weitere MUX 2:1 ergänzen muss:

Abb. A.6: MUX 2 × 4:4 aus MUX 2:1

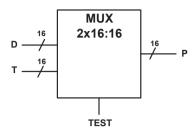

Aufgabe 43 Skizzieren Sie, wie man einen Multiplexer einsetzen könnte, um wahlweise 16 Testsignale oder 16 Datensignale an Anschlusspins eines Bausteins zu leiten.

Abb. A.7: Gemultiplextes Herausführen zweier Busse auf Anschluss-Pins

Sowohl Datensignale D als auch Testsignale T besitzen eine Wortbreite von 16 Bits. Ebenso gibt es 16 Pins, auf die das Bündel P geführt wird. Weil lediglich zwischen zwei Bündeln D und T umgeschaltet werden soll, reicht zur Auswahl ein einziges Steuersignal TEST. Für TEST=0 wird D zu den Pins geleitet, für TEST=1 T.

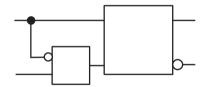

Aufgabe 44 Wie könnte man durch Beschaltung mit geeigneten Gattern aus einem "normalen" RS-Flipflop ein solches mit vorrangigem S-Eingang bekommen?

Die Beschaltung muss dafür sorgen, dass im Fall S'=R'=1 am Flipflop S=1 und R=0 entsteht. Andererseits dürfen andere Eingangsbelegungen nicht verändert werden.

Abb. A.8: Beschaltung eines RS-Flipflops für vorrangigen S-Eingang

Das kann durch ein Und-Gatter mit negiertem Eingang erreicht werden. Wenn S' = 1 ist, dann wird durch die Negation eine Null daraus. Ein Und-Gatter mit einer 0 an einem Eingang kann am Ausgang nichts anderes als eine 0 hervorbringen. Somit wird aus S' = R' = 1 tatsächlich am Flipflop S = 1 und R = 0.

S' wird nicht verändert. Also gilt immer S = S'. Wie man überprüfen kann, ergeben sich somit abhängig von S' und R' folgende Werte für S und R:

| S' | R' | S | R |

|----|----|---|---|

| 0  | 0  | 0 | 0 |

| 0  | 1  | 0 | 1 |

| 1  | 0  | 1 | 0 |

Tab. A.6: Umsetzung der Eingangswerte durch Gatterbeschaltung beim RS-Flipflop

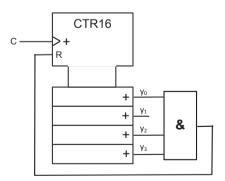

**Aufgabe 45** Konstruieren Sie einen Zähler, der bis 12 zählt und dann wieder bei 0 beginnt. Verwenden Sie dafür einen CTR16.

Die Zählfolge soll also die folgende sein:

Tab. A.7: Zählfolge eines Modulo-12-Zählers

| dez. | y <sub>3</sub> | $y_2$ | $y_1$ | $y_0$ |

|------|----------------|-------|-------|-------|

| 0    | 0              | 0     | 0     | 0     |

| 1    | 0              | 0     | 0     | 1     |

| 2    | 0              | 0     | 1     | 0     |

| 3    | 0              | 0     | 1     | 1     |

| 4    | 0              | 1     | 0     | 0     |

| 5    | 0              | 1     | 0     | 1     |

| 6    | 0              | 1     | 1     | 0     |

| 7    | 0              | 1     | 1     | 1     |

| 8    | 1              | 0     | 0     | 0     |

| 9    | 1              | 0     | 0     | 1     |

| 10   | 1              | 0     | 1     | 0     |

| 11   | 1              | 0     | 1     | 1     |

| 12   | 1              | 1     | 0     | 0     |

| (13  | 1              | 1     | 0     | 1)    |

Der Zählerstand 13 kann verwendet werden, um den Zähler auf 0 zurückzusetzen: sobald dieser Wert erscheint, wird ein Impuls auf einen asynchronen Rücksetzeingang gegeben, und der Zähler startet wieder bei 0.

Abb. A.9: Modulo-12-Zähler

Den Zählerstand 13 kann man mit Hilfe eines Und-Gatters erkennen. Eigentlich müsste man ein Und-Gatter mit 4 Eingängen nehmen, wobei  $y_1$  zu invertieren wäre, weil es beim Zählerstand 13 Null ist. Wenn wir aber die Tab. A.7 genauer ansehen, dann stellen wir fest, dass 13 der erste Zählerstand ist, bei dem  $y_0 = y_2 = y_3$  gilt. Es reicht also, nur diese drei Eingänge zu testen. So kommt man auf die Schaltung in Abb. A.9.

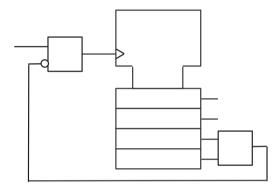

Aufgabe 46 Konstruieren Sie für eine Abpackmaschine einen Zähler, der beim Zählerstand 12 stehen bleibt. Verwenden Sie dafür einen CTR16.

Diesmal soll der Zähler bei 12 stehen bleiben. Die 13 wird also gar nicht mehr erreicht. Daher decodieren wir die 12. Sobald sie erkannt wird, also am Ausgang des rechten Und-Gatters eine 1 erscheint, werden durch die Negation am linken Und-Gatter weitere Zähltakte blockiert, denn am Ausgang des rechten Und-Gatters kann nur noch eine Null entstehen.

Abb. A.10: Zähler, der bei 12 stehenbleibt

Der Zähler sollte auch die Möglichkeit bieten, wieder rückgesetzt zu werden und von vorn zu beginnen. Daher wäre es sinnvoll, einen asynchronen Rücksetzeingang beim Zähler vorzusehen, der zum Rücksetzen mit einem Taster kurzzeitig mit 1 verbunden werden kann.

**Aufgabe 47** Welcher Wertebereich ergibt sich für 16- und 32-Bit-Zahlen in der Vorzeichen-Betrags-Darstellung?

Bei n Bits (incl. Vorzeichen) lassen sich Zahlen von  $-2^{n-1} + 1$  bis  $+2^{n-1} - 1$  darstellen. Für n=16 ergibt sich  $-2^{15} + 1$  ..  $+2^{15} - 1$  bzw. -32767 .. +32767.

Für n=32 bekommt man  $-2^{31} + 1 ... + 2^{31} - 1$  bzw. -2 147 483 647 ... + 2 147 483 647.

**Aufgabe 48** Stellen Sie die Zahl (-23)<sub>10</sub> als Dualzahl in der Vorzeichen-Betrags-Darstellung mit 7 Bit und mit 9 Bit Wortbreite dar!

$(23)_{10} = (10111)_2$

Dieses Umwandlungsergebnis (z.B. aus dem Taschenrechner) ist vorzeichenlos.

Wir wollen zunächst eine vorzeichenbehaftete Zahl mit 7 Bits Wortbreite. Ein Bit wird für das Vorzeichen verwendet. Das oben stehende vorzeichenlos Umwandlungsergebnis benötigt 5 Bits. Es ist also noch 1 Bit aufzufüllen. Das geschieht durch Einfügen von Nullen nach dem Vorzeichenbit. somit bekommt man:

$$(-23)_{10}$$

= $(1\ 0\ 10111)_{2\ VZB}$

Vorzeichenbit und aufgefülltes Bit sind mit Abständen gekennzeichnet.

Eine 9-Bit-Zahl bekommt man, wenn man weitere Nullen einfügt:

$$(-23)_{10}$$

= $(1\ 000\ 10111)_{2\ VZB}$

**Aufgabe 49** Stellen Sie die Zahl (-23)<sub>10</sub> als Dualzahl in der Einerkomplement-Darstellung mit 7 Bit und mit 9 Bit Wortbreite dar!

$$(23)_{10} = (10111)_2$$

Wir wollen eine 7-Bit-Zahl im Einerkomplement. Für die Umwandlung gibt es zwei Alternativen:

a) Wir wandeln zuerst ins Einerkomplement um und füllen dann mit Einsen auf 7 Bits auf:

(23)<sub>10</sub> = (10111)<sub>2</sub> ist vorzeichenlos! Wenn wir das direkt invertieren würden, also zu (01000)<sub>2 EK</sub> umwandeln würden, dann würde uns ein Bit für das Vorzeichen fehlen. Das Umwandlungsergebnis hätte eine führende Null, wäre also positiv. Daran könnte man erkennen, dass etwas schief gegangen sein muss.

Wir müssen also vor der Umwandlung (mindestens) eine führende Null ergänzen:

$$(23)_{10} = (010111)_2$$

$(-23)_{10} = (101000)_{2 \text{ EK}}$

Zum Auffüllen auf die gewünschte Wortbreite werden Einsen zwischen MSB und nachfolgenden Bits eingefügt. In unserem Fall ist es genau eine Eins, was mit Abständen gekennzeichnet ist:

$$(-23)_{10} = (1\ 01000)_{2\ EK} = (1\ 1\ 01000)_{2\ EK}$$

Insgesamt ist das eher umständlich und fehlerträchtig. Einfacher ist folgende Alternative:

b) Wir füllen die vorzeichenlose Zahl zuerst mit Nullen auf und wandeln sie dann ins Einerkomplement um

$$(23)_{10} = (10111)_2 = (0010111)_2$$

$(-23)_{10} = (1101000)_{2 \text{ EK}}$

Eine 9-Bit-Zahl bekommt man, wenn man zwei weitere Einsen einfügt, nach dem MSB also insgesamt drei:

$$(-23)_{10}$$

=  $(1\ 111\ 01000)_{2\ EK}$

**Aufgabe 50** Bilden Sie das Einerkomplement von (CACA0)<sub>16</sub> mit einer Wortbreite von 32 Bit.

32 Bit sind 8 Nibbles (Halbbytes) zu je 4 Bits. Jedes davon entspricht einer Hexadezimalziffer.

Wir ergänzen (CACA0)<sub>16</sub> somit auf 8 Stellen: (000CACA0)<sub>16</sub>.

Dann invertieren wir: (FFF3535F)<sub>16 EK</sub>

**Aufgabe 51** Stellen Sie die Zahl (–23)<sub>10</sub> als Dualzahl in der Zweierkomplement-Darstellung mit 7 Bit und mit 9 Bit Wortbreite dar!

$$(-23)_{10}$$

=  $(1101000)_{2 \text{ EK}}$  =  $(1101001)_{2 \text{ ZK}}$

bzw. mit 9 Bit Wortbreite:

$$(-23)_{10}$$

=  $(1\ 111\ 01000)_{2\ EK}$  =  $(1\ 111\ 01001)_{2\ ZK}$

Aufgabe 52 Bilden Sie das Zweierkomplement von (CACA0)<sub>16</sub> mit einer Wortbreite von 32 Bit.

$$(FFF3535F)_{16 EK} = (FFF35360)_{16 ZK}$$

Aufgabe 53 Kontrollieren Sie den angegebenen Wertebereich für den Datentyp long long.

Bei n Bits (incl. Vorzeichen) lassen sich unter Verwendung des Zweierkomplements Zahlen von  $-2^{n-1}$  bis  $+2^{n-1}-1$  darstellen.

Für n=64 ergibt sich  $-2^{63}$  ..  $+2^{63} - 1$  bzw.

-9 223 372 036 854 775 808 .. +9 223 372 036 854 775 807.

Aufgabe 54 Zeigen Sie, wie man die Bits 4 und 7 eines 8-Bit-Registers löscht, die Bits 0, 3 und 6 setzt und ferner die Bits 1, 2 und 5 invertiert.

Man führt Verknüpfungen mit folgenden Bitmasken durch:

AND 01101111 OR 01001001 XOR 00100110

#### **Aufgabe 55** Führen Sie folgende Rechnungen mit vorzeichenlosen Zahlen durch:

a)  $(0100)_2 + (1000)_2$

Wertigkeit

3

2

1

0

Operand 1:

0

1

0

0

Operand 2:

+

1

0

0

0

Ergebnis:

1

1

0

0

b)  $(1101)_2 + (10001)_2$

Wertigkeit Operand 1: Operand 2:  $+1_{1}$  $0_1$  $0_1$  $0_1$ Ergebnis:

c)  $(10110100)_2 + (00010111)_2$

Wertigkeit Operand 1: Operand 2: Ergebnis:

d)  $(10011101)_2 + (11011011)_2 + (00101010)_2$

Wertigkeit Operand 1: Operand 2: Operand 3:  $+ 0_1$  $0_1$  $1_{1+1}$  0  $0_1$  $1_1$ Ergebnis:

e)  $(BEEF)_{16} + (1CF7)_{16}$

Wertigkeit 3 2 1 0

Operand 1: B E E F

Operand 2:  $+1_1$   $C_1$   $F_1$  7

Ergebnis: D B E 6

f)  $(A03FD)_{16} + (46EA)_{16}$

Wertigkeit

4

3

2

1

0

Operand 1:

A

0

3

F

D

Operand 2:

+

4

6<sub>1</sub>

E<sub>1</sub>

A

Ergebnis:

A

4

A

E

7

**Aufgabe 56** Führen Sie folgende Rechnungen mit vorzeichenlosen Zahlen durch:

a)  $(1101)_2 - (1010)_2$

Wertigkeit

3

2

1

0

Operand 1:

1

1

0

1

Operand 2:

1

0

1

0

Ergebnis:

0

0

1

1

b)  $(1000)_2 - (0111)_2$

Wertigkeit

3

2

1

0

Operand 1:

1

0

0

0

Operand 2:

0<sub>1</sub>

1<sub>1</sub>

1<sub>1</sub>

1

Ergebnis:

0

0

0

1

c)  $(10011101)_2 - (00011011)_2 - (00100010)_2$

Wertigkeit 6 5 1 Operand 1: 0 1 0 1 Operand 2: - 0 0 0 1 1 0 1 1 0 Operand 3: Ergebnis:

d)  $(4CF5)_{16} - (30EB)_{16}$

Wertigkeit

3

2

1

0

Operand 1:

4

C

F

5

Operand 2:

3

0

E<sub>1</sub>

B

Ergebnis:

1

C

0

A

Aufgabe 57 Wie groß wäre das Multiplikationsergebnis allgemein, wenn man den letzten Schiebeschritt vergessen würde?

Weil der letzte Schiebeschritt ein Rechtsschieben ist, wäre das Ergebnis doppelt so groß wie der korrekte Wert.

**Aufgabe 58** Führen Sie die Multiplikation  $(14)_{10}$  ·  $(10)_{10}$  mit vorzeichenlosen 4-Bit-Zahlen im Dualsystem mit beiden Algorithmen durch.

### Verfahren 1:

|            |   |   |    |    |   | Op | <b>o</b> 1 |   |   |   | $O_{J}$ | р2 |     |                  |

|------------|---|---|----|----|---|----|------------|---|---|---|---------|----|-----|------------------|

| Wertigkeit |   |   |    |    |   |    |            |   |   |   | 3       | 2  | 1   | 0                |

|            |   |   |    |    |   | 1  | 1          | 1 | 0 | • | 1       | 0  | 1   | 0                |

| ZE         |   | 0 | 0  | 0  | 0 | 0  | 0          | 0 | 0 | - |         |    |     | ¥ keine Addition |

|            | + |   |    |    | 1 | 1  | 1          | 0 | 0 |   |         |    | 7   | ADD ZE, Op1'     |

| $ZE_{neu}$ |   | 0 | 0  | 0  | 1 | 1  | 1          | 0 | 0 |   |         | Z  | ke  | ine Addition     |

|            | + |   | 11 | 11 | 1 | 0  | 0          | 0 | 0 | _ | 7       | AD | D Z | ZE, Op1""        |

|            |   | 1 | 0  | 0  | 0 | 1  | 1          | 0 | 0 | - |         |    |     |                  |

#### Verfahren 2:

|            | Op   | 1 |   |   |   |   |   |   |   | Op2           |

|------------|------|---|---|---|---|---|---|---|---|---------------|

| Wertigkeit |      |   |   |   |   |   |   |   |   | 3 2 1 0       |

|            | 1    | 1 | 1 | 0 |   |   |   |   | • | 1 0 1 0       |

| ZE         | 0    | 0 | 0 | 0 |   |   |   |   | = | ש SHR ZE, 1   |

| $ZE_{neu}$ | 0    | 0 | 0 | 0 | 0 |   |   |   |   | ⊿ ADD ZE, Op1 |

|            | + 1  | 1 | 1 | 0 |   |   |   |   |   |               |

| ZE'        | 1    | 1 | 1 | 0 | 0 |   |   |   |   | SHR ZE, 1     |

| $ZE_{neu}$ | 0    | 1 | 1 | 1 | 0 | 0 |   |   |   | ש SHR ZE, 1   |

| $ZE_{neu}$ | 0    | 0 | 1 | 1 | 1 | 0 | 0 |   |   | ☑ ADD ZE, Op1 |

|            | + 11 | 1 | 1 | 0 |   |   |   |   |   |               |

|            |      | 1 |   |   |   |   |   |   |   |               |

| ZE'        | 1 0  | 0 | 0 | 1 | 1 | 0 | 0 |   |   | ש SHR ZE, 1   |

| $ZE_{neu}$ | 1    | 0 | 0 | 0 | 1 | 1 | 0 | 0 |   |               |

$(129)_{10} = (10000001)_2$

**Aufgabe 59** Führen Sie die Ganzzahl-Division (129)<sub>10</sub> : (14)<sub>10</sub> mit vorzeichenlosen Dualzahlen (8 bzw. 4 Bit) durch. Woran bemerkt man, dass die Division nicht aufgeht?

Wir haben eine Division mit m = 4 Bit Divisor. Daher ist die Division nach 4 Schritten beendet. Wenn die Division aufgeht, ist der Akku zu diesem Zeitpunkt Null. In unserem Falle steht dort aber  $(0011)_2 = 3$ . Das ist der Divisionsrest, denn  $9 \cdot 14 = 126$ . 129:14 ist somit 9 Rest 3.

Aufgabe 60 Führen Sie folgende Berechnungen in der Vorzeichen-Betrags-Darstellung und im Zweierkomplement durch. Verwenden Sie dabei das Dualsystem und 8-Bit-Zahlen (incl. Vorzeichen). Kontrollieren Sie jeweils das Ergebnis, wo sinnvoll.

Zunächst wandeln wir die verwendeten Zahlen ins Dualsystem, diejenigen, die auch mit negativem Vorzeichen vorkommen, außerdem ins Zweierkomplement.

$$\begin{array}{l} (18)_{10} = (00010010)_2, (-18)_{10} = (11101101)_{2 \text{ EK}} = (11101110)_{2 \text{ ZK}} \\ (27)_{10} = (00011011)_2 \\ (51)_{10} = (00110011)_2, (-51)_{10} = (11001100)_{2 \text{ EK}} = (11001101)_{2 \text{ ZK}} \\ (112)_{10} = (01110000)_2, (-112)_{10} = (10001111)_{2 \text{ EK}} = (10010000)_{2 \text{ ZK}} \end{array}$$

a) -51 + 18 = ?

Vorzeichen-Betragsdarstellung:

$Z_1$  ist negativ,  $Z_2$  ist positiv, also dritter Fall der Tabelle 11.1.

$$|E| = ||Z_1| - |Z_2||$$

Negativer Operand ist der betragsmäßig größere von beiden, also Ergebnisvorzeichen negativ. Das Ergebnis lautet  $E = (1\ 0100001)_2 = (-33)_{10}$ .

#### Zweierkomplement:

$$Z_{1}: \qquad 1 \qquad 1 \qquad 0 \qquad 0 \qquad 1 \qquad 1 \qquad 0 \qquad 1 \qquad = (-51)_{10}$$

$$Z_{2}: \qquad + \qquad 0 \qquad 0 \qquad 0 \qquad 1 \qquad 0 \qquad 0 \qquad 1 \qquad 0 \qquad = (+18)_{10}$$

$$E_{ZK}: \qquad \frac{1 \qquad 1 \qquad 0 \qquad 1 \qquad 1 \qquad 1 \qquad 1 \qquad 1 \qquad 1}{1 \qquad 1 \qquad 0 \qquad 1 \qquad 1 \qquad 1 \qquad 1 \qquad 1} \qquad = (+33)_{10}$$

$$\Rightarrow E = (-33)_{10}$$

#### b) 18 + 27 = ?

Addition zweier positiver Zahlen, kein Unterschied zwischen VZB, ZK und vorzeichenloser Darstellung!

c)

$$27 - 18 = ?$$

Vorzeichen-Betragsdarstellung:

$Z_1$  ist positiv,  $Z_2$  ist negativ, also zweiter Fall der Tabelle 11.1.

Positiver Operand ist der betragsmäßig größere von beiden, also Ergebnisvorzeichen positiv.

Das Ergebnis lautet  $E = (0\ 0001001)_2 = (+9)_{10}$ .

Zweierkomplement:

Vorzeichen-Betragsdarstellung:

$Z_1$  ist negativ,  $Z_2$  ist negativ, also vierter Fall der Tab. 11.1.

$$\begin{split} |E| &= |Z_1| + |Z_2| \\ &|Z_1|: \quad 1 \quad 1 \quad 1 \quad 0 \quad 0 \quad 0 \quad 0 \quad = (112)_{10} \\ &|Z_2|: \quad + \quad 0_1 \quad 0_1 \quad 1 \quad 0 \quad 0 \quad 1 \quad 0 \quad = (18)_{10} \\ &|E|: \quad 1 \quad 0 \quad 0 \quad 0 \quad 0 \quad 1 \quad 0 \quad = (130)_{10} \\ \ddot{\text{Uberlauf!}} \text{ Ergebnis ung\"{ultig!}} \end{split}$$

Zweierkomplement:

$$Z_1$$

: 1 0 0 1 0 0 0 0 0 =  $(-112)_{10}$

$Z_2$ :  $+_1$  1 1 1 0 1 1 1 0 =  $(-18)_{10}$

$E_{ZK}$ : 1 0 1 1 1 1 1 0 =  $(+9)_{10}$

Überlauf! Ergebnis ungültig!

**Aufgabe 61** Führen Sie die Multiplikation  $10 \cdot 6 = 60$  im Dualsystem mit Hilfe des Algorithmus aus Kapitel 10.2 (Verfahren 2) durch.

**Aufgabe 62** Welche Werte dürfen die Exponenten annehmen, wenn man die Charakteristik 8 Bits groß macht und die Konstante  $K_0 = 127$  nimmt?

Ch := E + K<sub>0</sub>

$$\Rightarrow$$

E = Ch - K<sub>0</sub>

8 Bit Charakteristik  $\Rightarrow$  0  $\leq$  Ch  $\leq$  255

$\Rightarrow$  0 - K<sub>0</sub>  $\leq$  E  $\leq$  255- K<sub>0</sub>

$\Rightarrow$  -127  $\leq$  E  $\leq$  +128

**Aufgabe 63** Welchen darstellbaren Zahlenbereich erhält man für 8 Bit Charakteristik und  $K_0 = 127$ , falls die Basis B=2 ist und die Zahlen normalisiert sind?

Bei normalisierten Zahlen bewegt sich der Betrag der Mantisse zwischen 0 und 1, weil der Vorkommateil Null ist: 0 < |M| < 1.

Die 0.0 ist zwar definitionsgemäß nicht normalisiert. Sie fällt aber in den darstellbaren Zahlenbereich. Somit gilt  $0 \le |M| < 1$ .

Der darstellbare Zahlenbereich wird also durch den Exponenten bestimmt. Wie aus Aufgabe 16 hervorgeht, gilt:

$$-127 \le E \le +128$$

.

Wegen der Basis B=2 gilt

$$2^{-127} \le 2^{E} \le 2^{+128}$$

.

$2^{E}$  ist der Faktor, mit dem die Mantisse multipliziert wird, um die Gleitkommazahl  $Z = M \cdot B^{E}$  zu erhalten. Dieser Faktor liegt zwischen  $2^{-127}$ , also ungefähr Null, und  $2^{+128} \approx 3,403 \cdot 10^{38}$ . Der Mantissenbetrag liegt zwischen 0 und 1, die Mantisse somit zwischen -1 und +1.

Also liegt Z zwischen  $-3,403 \cdot 10^{38}$  und  $+3,403 \cdot 10^{38}$ . Das ist auch der darstellbare Zahlenbereich.

Aufgabe 64 Wieviele gültige (Nachkomma-)Stellen bezogen auf das Dezimalsystem besitzt eine float-Variable maximal, und wieviele eine double-Variable? Welche Auswirkungen kann das in der Praxis haben?

Mit m Mantissenbits lassen sich  $2^m$  verschiedene Werte darstellen. Dazu benötigt man  $n = lg(2^m)$  Dezimalstellen. Es gilt:

$$n = \lg(2^m) = m \lg 2$$

Bei float beträgt m=23, somit n  $\approx$  6,92 oder abgerundet 6 gültige Stellen.

Double verwendet m=52 Mantissenbits, was n ≈ 15,65 oder 15 gültige Stellen ergibt.

Möchte man beispielsweise mit Geldbeträgen im Bereich von 10.000,00 Euro und mehr rechnen, ergeben sich bei Verwendung von float-Variablen Ungenauigkeiten. Stattdessen sollte man double-Variablen einsetzen.

Entsprechendes gilt, wenn die dargestellten Zahlen zwar keine allzu hohe Genauigkeit benötigen, aber z.B. viele tausend Male in einer Schleife miteinander verrechnet werden. Hier können sich die Ungenauigkeiten aufaddieren.

Aufgabe 65

Wandeln Sie folgende Zahlen in Dualbrüche mit 8 Bit Mantissenbetrag und 4 Bit Charakteristik, kein Hidden Bit, um. Wählen Sie einen sinnvollen Wert für K<sub>0</sub>. Machen Sie die Probe und geben Sie den absoluten Umwandlungsfehler an.

a) 65,625

$$(65)_{10} = (1000001)_2$$

$0,625 \cdot 2 = 1 + 0,25$

$0,25 \cdot 2 = 0 + 0,5$

$0,5 \cdot 2 = 1 + 0,0$

An dieser Stelle können wir mit der Umwandlung aufhören, weil Multiplikation von 0,0 nur 0,0 ergeben kann. Somit würden wir lediglich Nullen ans Ende des Nachkommateils anhängen. Wir lesen die Bits von oben nach unten und normalisieren:

$$x_W = (65,625)_{10} = (1000001,101)_2 = (0,1000001101)_2 \cdot 2^7$$

Weil das Komma 7 Stellen nach links verschoben wird, müssen wir mit einem Faktor 2<sup>7</sup> ausgleichen. Nun schneiden wir nach der achten Nachkommastelle ab, so dass die oben fettgedruckte 0 und 1 wegfallen:

$$x = (0.10000011)_2 \cdot 2^7$$

Die 4-Bit-Charakteristik läuft von 0 ... 15. Es wird somit sinnvollerweise  $K_0 := 7$  gewählt. Damit ergibt sich für die Charakteristik:

$$Ch = K_0 + E = 7 + 7 = 14 = (1110)_2$$

Die Zahl steht also so im Gleitpunktregister:

| 0     | 10000011 | 1110 |

|-------|----------|------|

| Vz(M) | M        | Ch   |

Wir machen nun die Probe:

$$x = (0.10000011)_2 \cdot 2^{14-7} = (2^{-1} + 2^{-7} + 2^{-8}) \cdot 2^7 = 2^6 + 2^0 + 2^{-1} = 65.5$$

$$\Delta x = x - x_W = 65.5 - 65.625 = -0.125 = -2^{-3}$$

Das Ergebnis ist also um ein Achtel zu klein. Das ist genau der Wert der Eins, die nicht mehr in den Mantissenbetrag passte.

b) 65,675

$$(65)_{10} = (1000001)_2$$

$$0,675 \cdot 2 = 1 + 0,35$$

$$0,35 \cdot 2 = 0 + 0,7$$

$$0,7 \cdot 2 = 1 + 0,4$$

$$0,4 \cdot 2 = 0 + 0,8$$

$$0,8 \cdot 2 = 1 + 0,6$$

$$0,6 \cdot 2 = 1 + 0,2$$

$$0,2 \cdot 2 = 0 + 0,4$$

$$0,4 \cdot 2 = 0 + 0,8$$

. . .

Wir stellen fest, dass sich der fett gedruckte Teil wiederholt. Sowohl ganzzahliger Anteil des Ergebnisses als auch Nachkommateil, nämlich 0 + 0,8, tauchen erneut auf. also müssen sich auch die nachfolgenden Zeilen der Umwandlung wiederholen. Es handelt sich also um einen *periodischen* Dualbruch. Das Umwandlungsergebnis lautet somit:

$$x_w = (65,675)_{10} = (1000001,101 \overline{0110})_2 = (0,1000001101 \overline{0110})_2 \cdot 2^7$$

Zur Normalisierung verschieben wir das Komma wieder um 7 Stellen nach links und gleichen mit dem Faktor  $2^7$  aus.

Bei einem periodischen Dualbruch kann die Mantisse beliebig lang sein, trotzdem werden unendlich viele Nachkommastellen abgeschnitten. Es entsteht also *immer* ein Umwandlungsfehler, schon bevor mit der Zahl gerechnet wird. Das liegt nicht am Dualsystem, denn in jedem Zahlensystem gibt es periodische Brüche mit unendlich vielen Stellen, denen endliche Brüche in anderen Zahlensystemen entsprechen können. Wir schneiden nun ab und erhalten:

$$x = (0,10000011)_2 \cdot 2^7$$

Wir stellen fest, dass dieses x den gleichen Wert hat wie das aus Aufgabe a). Mehr zu den Konsequenzen siehe Aufgabe d).

Entsprechend stimmen auch Vorzeichen und Charakteristik überein. Wieder steht also im Gleitkommaregister:

| 0 10000011 |   | 1110 |

|------------|---|------|

| Vz(M)      | M | Ch   |

Wieder machen wir die Probe:

$$x = 65.5$$

(wie oben)

$$\Delta x = x - x_W = 65.5 - 65.675 = -0.175$$

Obwohl wir unendlich viele Bits abgeschnitten haben, also auch unendlich viele Einsen, ist der entstehende Fehler dennoch endlich und vergleichsweise klein.

#### c) 0.025

Diesmal haben wir als Vorkommateil Null, können uns also dessen Umwandlung sparen. Wir wandeln den Nachkommateil um:

$$\begin{array}{lll} 0,025 & \cdot 2 = 0 + 0,05 \\ 0,05 & \cdot 2 = 0 + 0,1 \\ 0,1 & \cdot 2 = 0 + 0,2 \\ 0,2 & \cdot 2 = \mathbf{0} + \mathbf{0},\mathbf{4} \\ 0,4 & \cdot 2 = \mathbf{0} + \mathbf{0},\mathbf{8} \\ 0,8 & \cdot 2 = \mathbf{1} + \mathbf{0},\mathbf{6} \\ 0,6 & \cdot 2 = \mathbf{1} + \mathbf{0},\mathbf{2} \\ 0,2 & \cdot 2 = 0 + 0,4 \end{array}$$

...

Auch hier erkennen wir eine Periodizität. Es gilt:

$$x_w = (0.025)_{10} = (0.000\overline{0011})_2$$

Beim Normalisieren stoßen wir auf ein Problem: Das Komma müsste um 5 Stellen nach rechts verschoben werden, unter die Periode. Wie kann man mit so etwas umgehen? Ein kleiner Trick ist, eine der Perioden explizit hinzuschreiben. Die Periode wiederholt sich trotzdem noch unendlich oft. Dann können wir das Komma verschieben:

$$x_w = (0.025)_{10} = (0.000\overline{0011})_2 = (0.0000011\overline{0011})_2$$

=  $(0.11\overline{0011})_2 \cdot 2^{-5}$

Zum Ausgleich für das fünfmalige Rechtsschieben, das die Mantisse um den Faktor 2<sup>5</sup> vergrößert, benötigen wir einen Faktor 2<sup>-5</sup>, der das wieder ausgleicht.

Nun können wir die Nachkommastellen abschneiden. Wieder haben wir das Problem, dass das inmitten der Periode geschehen müsste. Erneut lösen wir das Problem dadurch, dass wir die Periode ausschreiben. Wir müssen sie allerdings zweimal ausschreiben:

$$x_w = (0.11\overline{0011})_2 \cdot 2^{-5} = (0.1100110011\overline{0011})_2 \cdot 2^{-5}$$

$$\Rightarrow x = (0.11001100)_2 \cdot 2^{-5}$$

Wir berechnen die Charakteristik:

$$Ch = K_0 + E = 7 + (-5) = 2 = (0010)_2$$

Die Zahl steht also so im Gleitpunktregister:

| 0 11001100 |   | 0010 |

|------------|---|------|

| Vz(M)      | M | Ch   |

Wir machen nun die Probe:

$$x = (0.11001100)_2 \cdot 2^{2-7} = (2^{-1} + 2^{-2} + 2^{-5} + 2^{-6}) \cdot 2^{-5} = 2^{-6} + 2^{-7} + 2^{-10} + 2^{-11} = 0.02490234375$$

$$\Delta x = x - x_W = -9,765625 \cdot 10^{-5} \text{ (exakt)}$$

Man beachte: Bei der Berechnung von x sollte man möglichst alle Stellen angeben, weil sonst der Wert für  $\Delta x$  viel zu ungenau wird!

d) Vergleichen Sie die Ergebnisse aus Aufgabe a) und b) miteinander. Welche Probleme könnten sich daraus bei der Softwareentwicklung ergeben?

Wir können aus Aufgabe a) und b) entnehmen, dass für die hier betrachtete FPU gilt:

65,675 = 65,625 = 65,5, denn alle drei Werte werden auf denselben Gleitkommaregister-Inhalt abgebildet:

| 0     | 10000011 | 1110 |

|-------|----------|------|

| Vz(M) | M        | Ch   |

Das ist aus mathematischer Sicht offenkundig falsch. Es gibt unendlich viele Zahlen, die auf diesen Registerinhalt abgebildet werden und zwischen denen die FPU somit nicht unterscheiden kann. Bei m Mantissenbits gibt es 2<sup>m</sup> unterschiedliche Mantissen. Nur die Zahlenwerte, die diesen entsprechen, werden genau dargestellt. Alle anderen Zahlen werden auf diese 2<sup>m</sup> Mantissen abgebildet, wodurch ein Fehler entsteht. Man kann daher sagen, die meisten, nämlich unendlich viele Gleitkommazahlen, werden verkehrt dargestellt!

Das hat beispielsweise Auswirkungen auf Abbruchbedingungen. Man sollte Gleitkommazahlen nie auf Gleichheit testen, denn zum einen kann eine Gleichheit erkannt werden, die gar nicht gegeben ist, wie im beschriebenen Fall. Eine Anweisung

Aber auch das umgekehrte kann passieren: Das Umwandlungsergebnis ist mal dicht drüber, mal dicht unter dem Vergleichswert, aber nie identisch. Daher:

Man sollte nie auf Gleichheit von Gleitkommazahlen prüfen!

Aber auch Größenvergleiche sind kritisch. Bei folgender Abfrage

```

Falls 65,675 > 65,5 \text{ dann } \dots

```

wäre die Bedingung nicht erfüllt, obwohl sie mathematisch gesehen erfüllt wäre!

Man sollte ferner im Sinn behalten, dass es unendlich viele Zahlen gibt, die sich auf keinem üblichen Prozessor exakt darstellen lassen. Denn dazu bräuchte man wegen der Periodizität unendlich viele Mantissenbits, und das ist nicht machbar.

Denkbar wären zwar Rechenwerke, die die Darstellung von Perioden erlauben, aber auch das hätte seine Grenzen, denn es lassen sich keine Perioden beliebiger Länge in Hardware darstellen, sondern eine Obergrenze wäre vorgegeben. Außerdem wären Berechnungen damit sehr umständlich. Und es bleiben Zahlen wie  $\pi$  oder e, die unendlich viele Nachkommastellen haben, aber nicht periodisch sind.

#### Aufgabe 66 Gleitkommaaddition

Gegeben sei ein einfaches Gleitkommarechenwerk mit 1 Bit Vorzeichen Vz, 4 Bit Charakteristik Ch und 6 Bit Mantissenbetrag |M|. K<sub>0</sub> sei der Einfachheit halber gleich Null. Addieren Sie zum Akku den Op1 unter Verwendung folgender Inhalte:

|      | Vz | M      | Ch   |

|------|----|--------|------|

| Ak:  | 0  | 001001 | 1001 |

| Op1: | 0  | 101011 | 0111 |

- a) ohne vorher den Akkumulator zu normalisieren.

- 1) Charakteristikangleichung laut Tab. 14.3:

$$Ch(Ak) > Ch(Op1) \Rightarrow Ch(Op1)++, SHR |M(Op1)|$$

|      | Vz | M      | Ch   |

|------|----|--------|------|

| Ak:  | 0  | 001001 | 1001 |

| Op1: | 0  | 010101 | 1000 |

Hier wird ein Bit von Op1 hinaus geschoben!

$$Ch(Ak) > Ch(Op1) \Rightarrow Ch(Op1) ++, SHR |M(Op1)|$$

|      | Vz | M      | Ch   |

|------|----|--------|------|

| Ak:  | 0  | 001001 | 1001 |

| Op1: | 0  | 001010 | 1001 |

Ein weiteres Bit von Op1 verschwindet!

$$Ch(Ak) = Ch(Op1) \Rightarrow Charakteristikangleichung fertig$$

#### 2) Mantissenaddition

|                     | Vz | M              | Ch   |

|---------------------|----|----------------|------|

| Ak:                 | 0  | 001001         | 1001 |

| + Op1:              | 0  | 001010         | 1001 |

| Ak <sub>neu</sub> : | 0  | <b>0</b> 10011 | 1001 |

- 3) Vorzeichenermittlung: Beide Operanden positiv, Ergebnis ebenso

- 4) Normalisierung

$$MSB(M(Ak)) = 0 \Rightarrow SHL M(Ak), Ch(Ak) - -$$

|     | Vz | M      | Ch   |  |

|-----|----|--------|------|--|

| Ak: | 0  | 100110 | 1000 |  |

$MSB(M(Ak)) = 1 \Rightarrow Normalisierung beendet.$

Probe:

Die Rechnung sollte eigentlich folgendermaßen lauten:

Ak =

$$(001001)_2 \cdot 2^9 = (2^{-3} + 2^{-6})_2 \cdot 2^9 = 2^6 + 2^3 = 72$$

Op1 =  $(101011)_2 \cdot 2^7 = (2^{-1} + 2^{-3} + 2^{-5} + 2^{-6})_2 \cdot 2^7 = 2^6 + 2^4 + 2^2 + 2^1 = 86$

$\Rightarrow$  Summe  $x_W = (158)_{10} = (10011110)_2$

Wir haben erhalten:

$$x = Ak = (100110)_2 \cdot 2^8 = (2^{-1} + 2^{-4} + 2^{-5})_2 \cdot 2^8 = 2^7 + 2^4 + 2^3 = 152$$

Es gilt also:

$$\Delta x = x - x_W = 152 - 158 = -6$$

Das entspricht genau den beiden Bits von Op1, die bei der Charakteristikangleichung hinausgeschoben wurden. Sie hatten die Wertigkeiten –5 und –6 und wurden mit Charakteristik 7 multipliziert, also hatten sie den Wert  $(2^{-5} + 2^{-6}) \cdot 2^7 = 2^2 + 2^1 = 4+2 = 6$ .

b) mit vorheriger Normalisierung.

|      | Vz | M              | Ch   |

|------|----|----------------|------|

| Ak:  | 0  | <b>0</b> 01001 | 1001 |

| Op1: | 0  | <b>1</b> 01011 | 0111 |

1) Normalisierung: Der Kürze halber normalisieren wir beide Operanden gleichzeitig:

$$MSB(M(Ak)) = 0 \Rightarrow SHL M(Ak), Ch(Ak) - -$$

$MSB(M(Op1)) = 1 \Rightarrow Op1$  ist bereits normalisiert.

|      | Vz | M              | Ch   |

|------|----|----------------|------|

| Ak:  | 0  | <b>0</b> 10010 | 1000 |

| Op1: | 0  | 101011         | 0111 |

$$MSB(M(Ak)) = 0 \Rightarrow SHL M(Ak), Ch(Ak) - -$$

|      | Vz | M              | Ch   |

|------|----|----------------|------|

| Ak:  | 0  | <b>1</b> 00100 | 0111 |

| Op1: | 0  | 101011         | 0111 |

$MSB(M(Ak)) = = 1 \Rightarrow$  Normalisierung beendet.

Charakteristikangleichung laut Tab. 14.3:

Ch(Ak) = = Ch(Op1) ⇒ Die Charakteristiken sind bereits angeglichen.

#### 3) Mantissenaddition

|                     | Vz | M               | Ch   |

|---------------------|----|-----------------|------|

| Ak:                 | 0  | 100100          | 0111 |

| + Op1:              | 0  | 101011          | 0111 |

| Ak <sub>neu</sub> : | 0  | <b>1</b> 001111 | 0111 |

Es tritt ein Übertrag auf. Sinnvollerweise wird dieser als zusätzliches Mantissenbit aufgefasst. Somit wird die Mantisse rechtsgeschoben und die Charakteristik erhöht, damit das Übertragsbit in die Mantisse passt:

|     | Vz | M              | Ch   |

|-----|----|----------------|------|

| Ak: | 0  | <b>1</b> 00111 | 1000 |

- 4) Vorzeichenermittlung: Beide Operanden positiv, Ergebnis ebenso

- 5) Normalisierung

$MSB(M(Ak)) = 1 \Rightarrow Der Akku ist bereits normalisiert. Das Endergebnis lautet somit:$

|     | Vz | M      | Ch   |

|-----|----|--------|------|

| Ak: | 0  | 100111 | 1000 |

Probe:

$$x = Ak = (100111)_2 \cdot 2^8 = (2^{-1} + 2^{-4} + 2^{-5} + 2^{-6})_2 \cdot 2^8 = 2^7 + 2^4 + 2^3 + 2^2 = 156$$

Es gilt also:

$$\Delta x = x - x_W = 156 - 158 = -2$$

c) Vergleichen Sie die Ergebnisse von a) und b) im Hinblick auf ihre Genauigkeit!

Das Ergebnis von b) ist genauer als das Ergebnis von a). Bei a) wurden 2 Bits von Op1 hinausgeschoben, bei a) nur ein Bit von Ak, weil der Übertrag auftrat.

Die vorherige Normalisierung kann also das *unnötige* Hinausschieben von Bits verhindern. Normalisierung kann aber nicht in jedem Einzelfall verhindern, dass Bits verloren gehen, denn bei b) hätte man 7 Mantissenbits gebraucht, damit alle Einsen hineinpassen. Daran ändert auch vorherige Normalisierung nichts.

d) Variante: Nehmen Sie nun folgende Inhalte und rechnen Sie die Aufgabe nochmal durch. Vergleichen Sie die Auswirkungen.

|      | Vz | M      | Ch   |

|------|----|--------|------|

| Ak:  | 0  | 001001 | 1001 |

| Op1: | 0  | 001011 | 0111 |

### Wir führen die Rechnung zunächst wieder durch, ohne vorher den Akkumulator zu normalisieren.

1) Charakteristikangleichung laut Tab. 14.3:

$$Ch(Ak) > Ch(Op1) \Rightarrow Ch(Op1)++, SHR |M(Op1)|$$

|      | Vz | M      | Ch   |

|------|----|--------|------|

| Ak:  | 0  | 001001 | 1001 |

| Op1: | 0  | 000101 | 1000 |

Wieder wird ein Bit von Op1 hinaus geschoben!

$$Ch(Ak) > Ch(Op1) \Rightarrow Ch(Op1)++, SHR |M(Op1)|$$

|      | Vz | M      | Ch   |

|------|----|--------|------|

| Ak:  | 0  | 001001 | 1001 |

| Op1: | 0  | 000010 | 1001 |

Ein weiteres Bit von Op1 verschwindet!  $Ch(Ak) = Ch(Op1) \Rightarrow Charakteristikangleichung fertig$

#### 2) Mantissenaddition

|                     | Vz | M              | Ch   |

|---------------------|----|----------------|------|

| Ak:                 | 0  | 001001         | 1001 |

| + Op1:              | 0  | 000010         | 1001 |

| Ak <sub>neu</sub> : | 0  | <b>0</b> 01011 | 1001 |

- 3) Vorzeichenermittlung: Beide Operanden positiv, Ergebnis ebenso

- 4) Normalisierung

$$MSB(M(Ak)) = 0 \Rightarrow SHL M(Ak), Ch(Ak) - -$$

$$Vz | M| Ch$$

$$Ak: 0 101100 0111$$

$MSB(M(Ak)) = 1 \Rightarrow Normalisierung beendet.$

#### Probe:

Die Rechnung sollte eigentlich folgendermaßen lauten:

Ak =

$$(001001)_2 \cdot 2^9 = (2^{-3} + 2^{-6})_2 \cdot 2^9 = 2^6 + 2^3 = 72,0$$

Op1 =  $(001011)_2 \cdot 2^7 = (2^{-3} + 2^{-5} + 2^{-6})_2 \cdot 2^7 = 2^4 + 2^2 + 2^1 = 22,0$

$\Rightarrow$  Summe  $x_W = (94)_{10} = (10111110)_2$

Wir haben erhalten:

$$x = Ak = (101100)_2 \cdot 2^7 = (2^{-1} + 2^{-3} + 2^{-4})_2 \cdot 2^7 = 2^6 + 2^4 + 2^3 = 88$$

Es gilt also:

$$\Delta x = x - x_W = 88 - 94 = -6$$

Das entspricht genau den beiden Bits von Op1, die bei der Charakteristikangleichung hinausgeschoben wurden. Sie hatten die Wertigkeiten –5 und –6 und wurden mit Charakteristik 7 multipliziert, also hatten sie den Wert  $(2^{-5} + 2^{-6}) \cdot 2^7 = 2^2 + 2^1 = 4+2=6$ .

## Bei dem Schritt, der vorher der Aufgabe b) entsprach, wird nun zuerst normalisiert, bevor wir die Rechnung durchführen:

|      | Vz | M              | Ch   |

|------|----|----------------|------|

| Ak:  | 0  | <b>0</b> 01001 | 1001 |

| Op1: | 0  | 001011         | 0111 |

#### 1) Wir normalisieren zunächst nur den Akku.

$MSB(M(Ak)) = 0 \Rightarrow SHL M(Ak), Ch(Ak) - -$

|      | Vz | M              | Ch   |

|------|----|----------------|------|

| Ak:  | 0  | <b>0</b> 10010 | 1000 |

| Op1: | 0  | 001011         | 0111 |

$$MSB(M(Ak)) = 0 \Rightarrow SHL M(Ak), Ch(Ak) - -$$

|      | Vz | M              | Ch   |

|------|----|----------------|------|

| Ak:  | 0  | <b>1</b> 00100 | 0111 |

| Op1: | 0  | 001011         | 0111 |

$MSB(M(Ak)) = 1 \Rightarrow Die Normalisierung des Akkus ist nun beendet. Wir werden gleich sehen, dass es nichts bringen würde, den Op1 auch noch zu normalisieren.$

#### 2) Charakteristikangleichung

Es gilt: Ch(Ak) = Ch(Op1), die Charakteristiken sind also bereits angeglichen.

Den Op1 im vorigen Schritt auch noch zu normalisieren, hätte also nichts gebracht, denn dadurch wären die Charakteristiken wieder ungleich geworden. Die dann nötige Charakteristikangleichung hätte dies einfach wieder rückgängig gemacht.

3) Mantissenaddition

|                     | Vz | M              | Ch   |

|---------------------|----|----------------|------|

| Ak:                 | 0  | 100100         | 0111 |

| + Op1:              | 0  | 001011         | 0111 |

| Ak <sub>neu</sub> : | 0  | <b>1</b> 01111 | 0111 |

- 4) Vorzeichenermittlung: Beide Operanden positiv, Ergebnis ebenso

- 5) Normalisierung

$MSB(M(Ak)) = 1 \Rightarrow Der Akku ist bereits normalisiert. Das Endergebnis lautet somit:$

|     | Vz | M      | Ch   |

|-----|----|--------|------|

| Ak: | 0  | 101111 | 0111 |

Probe:

$$x = Ak = (101111)_2 \cdot 2^7 = (2^{-1} + 2^{-3} + 2^{-4} + 2^{-5} + 2^{-6})_2 \cdot 2^7 = 2^6 + 2^4 + 2^3 + 2^2 + 2^1 = 94$$

Das ist das exakte Ergebnis! Wir hatten ja auch keine Bits hinaus geschoben. Es gilt also:

$$\Delta x = x - x_W = 94 - 94 = 0$$

#### Vergleichen Sie die Ergebnisse im Hinblick auf ihre Genauigkeit!

Diesmal konnten wir durch die Normalisierung sogar verhindern, dass überhaupt ein Fehler aufgetreten ist. Das ist der Idealfall.

Aufgabe 67 Installieren Sie einen Disassembler mit HexDump-Funktionalität. Sehen Sie sich eine Binärdatei damit beachten Sie, dass manche Anmerkung: Bitte Software-Lizenzvereinbarungen das Disassemblieren der Software verbieten. Analysieren Sie also am besten eine selbst erzeugte Binärdatei.

Beispiele für geeignete Disassembler sind IDA Pro – Free, DDD, Kdbg, objdump, etc.

### Aufgabe 68

Ein Maschinenbefehl, der zuvor 5 Takte bzw. Mikrobefehle benötigt hat, wird durch eine Optimierung auf 3 Takte verbessert. Um wieviel Prozent verbessert sich dadurch seine Performance? Die Taktfrequenz des Prozessors betrage 2,6 GHz. Welche Taktfrequenz würde man benötigen, wenn man durch Erhöhung der Taktfrequenz denselben Effekt erzielen möchte?

Die Performance verbessert sich um (5-3)/5 = 40%.

Man müsste die Taktfrequenz um ebenfalls 40% erhöhen, also um  $0.4 \cdot 2.6$  GHz = 1.04 GHz auf 3.64 GHz.

Weil sich eine Optimierung eines einzelnen Maschinenbefehls nur anteilig auswirkt, ist diese Angabe aber nur sinnvoll, wenn alle Befehle des Befehlssatzes entsprechend verbessert werden.

### **Aufgabe 69** Welchen Inhalt muss also das Register in diesem Moment noch haben?

Der Adressmultiplexer leitet den Opcode zum Ausgang weiter. Also muss der Multiplexer an seinem Eingang A/B eine Null haben, damit B zum Ausgang durchgeschaltet wird.

Ein OR-Gatter hat genau dann eine 0 am Ausgang, wenn alle Eingänge 0 sind. Somit muss eine (0000)<sub>2</sub> im Register befinden. Sie stellt die Adresse des letzten Mikrobefehls des vorigen Maschinenbefehls dar, welche bei unserer Mikroprogrammsteuerung immer Null sein muss.

### **Aufgabe 70** Warum teilen sich alle Mikroprogramme die Adresse 0?

Weil ausschließlich die Adresse 0 als Endekennung zum Umschalten des Multiplexers verwendet wird. Weil jedes Mikroprogramm endet, wird schließlich irgendwann von jedem Mikroprogramm die Adresse 0 erreicht.

# Aufgabe 71 Könnte man mehrere unterschiedliche Adressen als Endekennung verwenden? Wenn ja, wie müsste man die Mikroprogrammsteuerung modifizieren, um das zu erreichen?

Ja. Man könnte z.B. die Adressen 0 und 1 als Endekennungen nehmen, mit jeweils unterschiedlichen aktivierten Steuersignalen.

Man bräuchte lediglich das niederwertigste Bit des Registers nicht auf das OR-Gatter zu führen. Dann würde es sowohl bei (0000)<sub>2</sub> als auch bei (0001)<sub>2</sub> auf den neuen Opcode umschalten. Würde man beide niederwertigsten Bits vom OR-Gatter trennen, hätte man 4 Endekennungen, nämlich die Adressen (0000)<sub>2</sub> bis (0011)<sub>2</sub>.

Aufgabe 72 Welche Maschinenbefehle sind außer dem betrachteten in der obigen Mikroprogrammsteuerung enthalten? Geben Sie die Opcodes, die der Reihe nach jeweils durchlaufenen Mikroprogrammadressen und die aktivierten Steuersignale an!

Am besten schaut man nach bisher nicht verwendeten Zeilen mit der Folgeadresse 0. Das könnten letzte Zeilen eines Mikroprogrammes sein, allerdings auch unbelegte Zeilen.

Dann arbeitet man sich "rückwärts" bis zur Startadresse des Mikroprogrammes vor. Die ist der Opcode des Maschinenbefehls. Man kann sie daran erkennen, dass kein Mikrobefehl sie als Folgeadresse hat.

Aus dem Beispiel wissen wir bereits, dass die Adressfolge 6 - 12 - 5 - 7 - 0 enthalten ist. In unserer Mikroprogrammsteuerung finden wir ferner die Adressfolgen:

$$2-1-3-8-0$$

$10-14-4-0$

$13-0$

$15-9-11-0$

Allerdings wäre es auch möglich, dass ein Mikroprogramm vollständig in einem anderen enthalten ist. Das könnte man auf diese Weise nicht entdecken. Z.B. träfe das auf einen möglicherweise existierenden Opcode 5 mit Adressfolge 5-7-0 zu.

Zu den neu gefundenen Adressfolgen gehören folgende Mikroprogramme:

### a) Opcode 2:

| Schritt | μPrg-<br>Adresse | Aktivierte Steuersignale | Folgeadresse |

|---------|------------------|--------------------------|--------------|

| 1       | 2                | A, H, L                  | 1            |

| 2       | 1                | E, K                     | 3            |

| 3       | 3                | D                        | 8            |

| 4       | 8                | D, G, J                  | 0            |

| 5       | 0                | X                        | (beliebig)   |

### b) Opcode 10:

| Schritt | μPrg-<br>Adresse | Aktivierte Steuersignale | Folgeadresse |

|---------|------------------|--------------------------|--------------|

| 1       | 10               | B, F, K                  | 14           |

| 2       | 14               | G                        | 4            |

| 3       | 4                | F, H, K                  | 0            |

| 4       | 0                | X                        | (beliebig)   |

# c) Opcode 13:

| Schritt | μPrg-<br>Adresse | Aktivierte Steuersignale | Folgeadresse |

|---------|------------------|--------------------------|--------------|

| 1       | 13               | C, E, J                  | 0            |

| 2       | 0                | X                        | (beliebig)   |

# d) Opcode 15:

| Schritt | μPrg-<br>Adresse | Aktivierte Steuersignale | Folgeadresse |

|---------|------------------|--------------------------|--------------|

| 1       | 15               | A, E, H                  | 9            |

| 2       | 9                | F                        | 11           |

| 3       | 11               | D, L                     | 0            |

| 4       | 0                | X                        | 0 (beliebig) |

Aufgabe 73 In den Zeilen 7 und 12 wird jeweils nur das Steuersignal I aktiviert. Beide Mikrobefehle bewirken also dasselbe. Könnte man die beiden Zeilen somit zu einer zusammenfassen?

Nein, denn die Folgeadressen stimmen nicht überein. Die Zeilen sind also nicht völlig identisch. Falls auch die Folgeadressen dieselben wären, könnte man die Zeilen zusammenfassen.

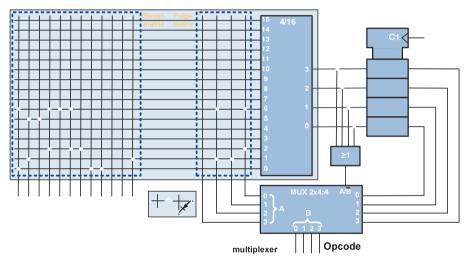

# Aufgabe 74 Mikroprogrammsteuerung

Es soll eine Mikroprogrammsteuerung konzipiert werden, die beim Maschinenbefehl mit dem Opcode 2 die angegebene Folge von Steuersignalen erzeugt. Skizzieren Sie eine Mikroprogrammsteuerung mit 16 Mikroprogrammadressen, die diese Aufgabe löst.

| Tab. A.8: | Folge von | Steuersignalen | einer Mikrop | rogrammsteuerung |

|-----------|-----------|----------------|--------------|------------------|

|           |           |                |              |                  |

| Schritt Nr. | Adresse | aktivierte Steuersignale | Folgeadresse |

|-------------|---------|--------------------------|--------------|

| 1           | ?       | D, F, G                  | 1            |

| 2           | 1       | B, L                     | 6            |

| 3           | 6       | A, D, E, F               | 5            |

| 4           | 5       | B, C                     | 0            |

| 5           | ?       | A, H, I                  | 0 (beliebig) |

Abb. A.11: Programmierte Mikroprogrammsteuerung

Aufgabe 75 Wie viele Spalten benötigt man bei 50 000 real vorkommenden Signalkombinationen in der Steuermatrix, wenn man eine Lookup Table einsetzt? Wie viele Spalten spart man gegenüber einer Funktionalbitsteuerung mit 500 Steuersignalen ein?

Man bildet den Zweierlogarithmus, also 1d 50 000, was aufgerundet 16 ergibt. Alternativ sieht man, dass 50 000 zwischen den Zweierpotenzen  $2^{15} = 32768$  und  $2^{16} = 65536$  liegt. Man benötigt also 16 Bits bzw. Spalten, um die Signalkombinationen durchzunummerieren.

Gegenüber den 500 Spalten von zuvor spart man 500 - 16 = 484 ein, das sind 484/500 = 96.8%.

Aufgabe 76 Wie kann man zwei Maschinenbefehle zu einer gemeinsamen Abarbeitung ihrer Mikrobefehle zusammenfassen?

In beiden Mikroprogrammen sieht man einen Mikrobefehl mit derselben Folgeadresse f vor. Ab dieser Mikrobefehlsadresse nutzen beide Mikroprogramme dieselben Zeilen der Koppelmatrix bzw. Mikrobefehlsadressen.

Aufgabe 77 Wie würde man vorgehen, wenn man vier ähnliche Maschinenbefehle teilweise zusammenfassen will, z.B. MOV AX/BX/CX/DX, []?

Das Zusammenfassen erfolgt wieder über eine gemeinsame Folgeadresse. Die Aufsplittung kann man anhand von zwei Opcode-Bits vornehmen, z.B.

| Opcode-LSBs | Operanden-<br>Ziel |

|-------------|--------------------|

| 00          | AX                 |

| 01          | BX                 |

| 10          | CX                 |

| 11          | DX                 |

### Aufgabe 78

Ein Prozessor besitze 500 unterschiedliche Maschinenbefehle in seinem Befehlssatz. Wie viele Bits müsste ein Opcode umfassen? Wie könnte man vorteilhaft vorgehen, wenn der Prozessor nur Zweierpotenzen als Bitanzahl für die Opcodes verwenden kann? Welche Wortbreite müssen die Mikroprogrammadressen mindestens besitzen, wenn ein Maschinenbefehl im Schnitt 8 Mikrobefehle umfasst? Welche Wortbreite benötigt man für die im Mikroprogrammspeicher abzulegenden Daten, wenn es 30.000 verschiedene Steuersignalkombinationen gibt?

ld 500 ergibt aufgerundet 9. Ein Opcode benötigt also 9 Bits. Das passt gerade nicht mehr in ein 8-Bit-Wort. Man könnte zwar ausschließlich 16-Bit-Opcodes verwenden, aber das wäre nicht allzu effizient. Daher würde man vorteilhaft so vorgehen:

Für häufig benötigte Opcodes verwendet man 8-Bit-Worte. Damit kann man 255 Opcodes abdecken, z.B. von 1 bis 255. Wählt man als Opcode-Byte die 0, dann ist das das Zeichen für den Prozessor, dass ein weiteres Opcode-Byte folgt. Somit werden die restlichen 500 - 255 = 245 Opcodes, und nur diese, 2 Bytes lang werden. Diese verwendet man für seltener benötigte Befehle.

Das ist ein ähnliches Verfahren wie bei den Telefonnummern. Man könnte alle Vorwahlen gleich lang machen, aber besser ist es, die häufig verwendeten Vorwahlen großer Städte, z.B. München, kurz zu halten (in diesem Beispiel 089). Im Gegenzug werden die Vorwahlen kleinerer Orte, zu denen weniger oft Verbindungen aufgebaut werden, als längere Ziffernfolgen konzipiert.

Der Prozessor hat 500 Maschinenbefehle zu je 8 Mikrobefehlen im Befehlssatz. Also umfasst die Mikroprogrammsteuerung  $500 \cdot 8 = 4000$  Mikrobefehle bzw. Mikroprogrammadressen. Die nächsthöhere Zweierpotenz ist  $2^{12} = 4096$ . Somit werden 12 Bit-Mikroprogrammadressen benötigt.

Für die 30000 Steuersignalkombinationen benötigt man 15 Bits, da die nächsthöhere Zweierpotenz  $2^{15} = 32768$  ist. Außer den Steuersignalen werden im Mikroprogrammspeicher auch noch die Folgeadressen abgelegt, die wie die Mikroprogrammadressen 12 Bit lang sind. An jeder Mikroprogrammadresse muss man somit 15 + 12 = 27 Bit ablegen.

Bei dem Mikrobefehlsspeicher handelt es sich somit um einen 4 kBit x 27 – Speicher. Er hat also insgesamt 4096 Adressen (aufgerundet), an denen sich jeweils ein 27-Bit-Datenwort befindet.

# **Aufgabe 79** Stellen Sie die wesentlichen Vor- und Nachteile der Mikroprogrammierung zusammen.

Tab. A.9: Vor- und Nachteile der Mikroprogrammierung

| Vorteile der Mikroprogrammierung                                       | Nachteile                        |

|------------------------------------------------------------------------|----------------------------------|

| Einheitliche Vorgehensweise                                            | langsam im Vergleich zum Schalt- |

| Dadurch einfacherer Entwurf von Prozessoren und geringere Entwick-     | werk                             |

| lungskosten                                                            |                                  |

| Hohe Flexibilität                                                      |                                  |

| Bei Einsatz von wiederbeschreibbaren Speichern einfache Fehlerbeseiti- |                                  |

| gung.                                                                  |                                  |

Aufgabe 80 Woher weiß der Prozessor, um welchen Wert der Befehlszeiger erhöht werden muss? Reicht einmaliges Erhöhen in jedem Falle aus? Begründung!

Anhand des Opcodes ist erkennbar, um wie viele Bytes der Befehlszeiger zu verändern ist, weil jeder Maschinenbefehl eine charakteristische Länge besitzt.

Werden Daten aus dem Hauptspeicher geholt oder Sprungbefehle ausgeführt, wird der Befehlszeiger in einer späteren Phase des Befehlszyklus nötigenfalls nochmals verändert.